ACS8530 Ver la hoja de datos (PDF) - Semtech Corporation

Número de pieza

componentes Descripción

Fabricante

ACS8530 Datasheet PDF : 152 Pages

| |||

ACS8530 SETS

Synchronous Equipment Timing Source for

Stratum 2/3E Systems

ADVANCED COMMUNICATIONS

Description

FINAL

Features

DATASHEET

The ACS8530 is a highly integrated, single-chip solution

for the Synchronous Equipment Timing Source (SETS)

function in a SONET or SDH Network Element. The device

generates SONET or SDH Equipment Clocks (SEC) and

Frame Synchronization clocks. The ACS8530 is fully

compliant with the required international specifications

and standards.

The device supports Free-run, Locked and Holdover

modes. It also supports all three types of reference clock

source: recovered line clock, PDH network, and node

synchronization. The ACS8530 generates independent

SEC and BITS clocks, an 8 kHz Frame Synchronization

clock and a 2 kHz Multi-Frame Synchronization clock.

Two ACS8530 devices can be used together in a Master/

Slave configuration mode allowing system protection

against a single ACS8530 failure.

A microprocessor port is incorporated, providing access to

the configuration and status registers for device setup

and monitoring. The ACS8530 supports IEEE 1149.1[5]

JTAG boundary scan.

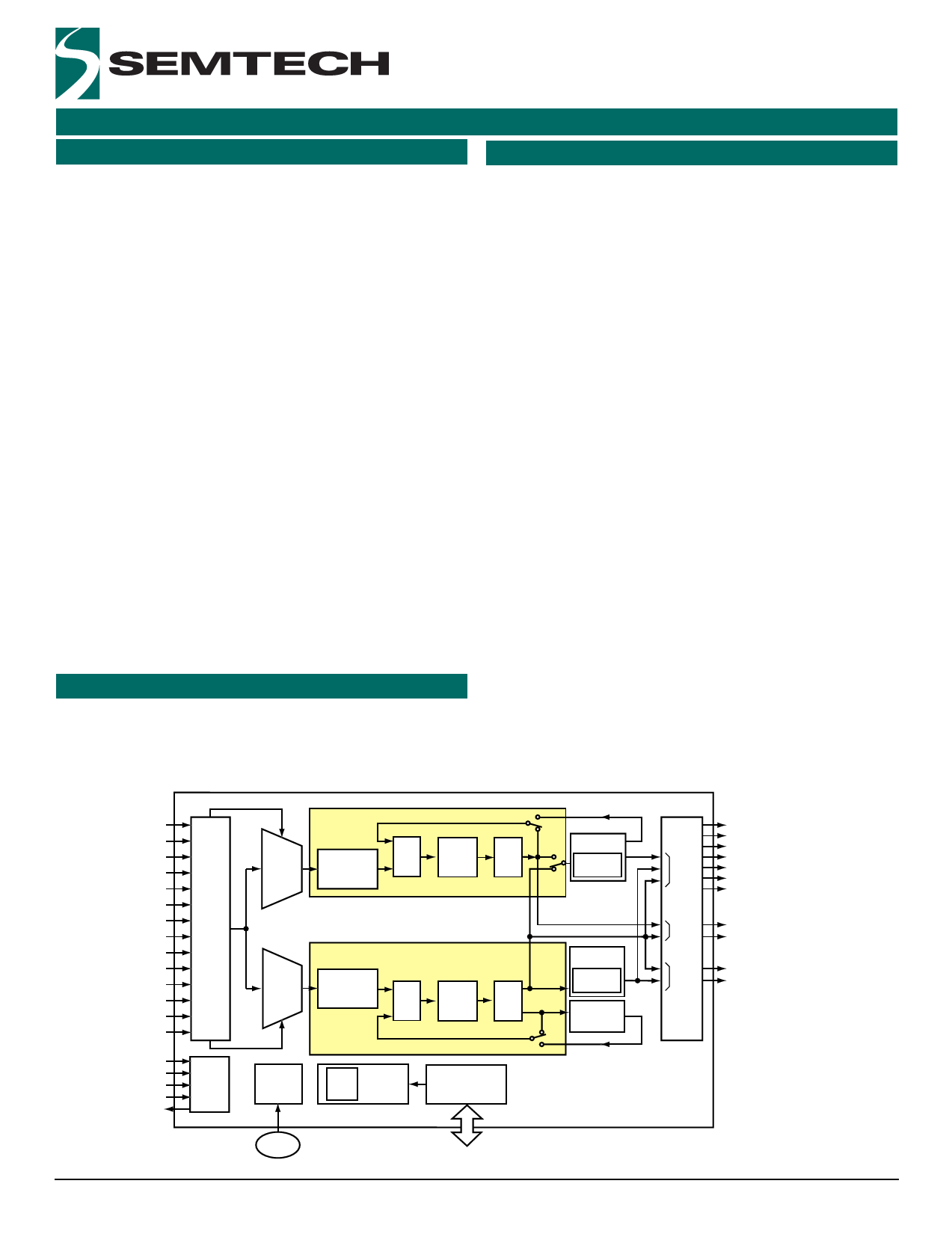

Block Diagram

Suitable for Stratum 2, 3E, 3, 4E and 4 and SONET

Minimum Clock (SMC) or SONET/SDH Equipment

Clock (SEC) applications (to Telcordia 1244-CORE[19]

Stratum 3E, and GR-253[17], and ITU-T G.812[10]

Type III and G.813[11] specifications)

Accepts 14 individual input reference clocks, all with

robust input clock source quality monitoring

Simultaneously generates nine output clocks, plus

two sync pulse outputs

Absolute Holdover accuracy better than 3 x 10-10

(manual), 7.5 x 10-14 (instantaneous); Holdover

stability defined by choice of external XO

Programmable PLL bandwidth, for wander and jitter

tracking/attenuation, 0.5 mHz to 70 Hz in 18 steps

Automatic hit-less source switchover on loss of input

Phase Transient Protection and Phase Build-out on

locked to reference and on reference switching

Microprocessor interface - Intel, Motorola, Serial,

Multiplexed, or boot from EPROM

Output phase adjustment in 6 ps steps up to ±200 ns

IEEE 1149.1 JTAG[5] Boundary Scan

Single 3.3 V operation. 5 V tolerant

Available in LQFP 100 package

Lead (Pb) - free version available (ACS8530T), RoHS

and WEEE compliant.

Figure 1 Block Diagram of the ACS8530 SETS

2 x AMI

10 x TTL

2 x PECL/LVDS

Programmable;

64/8 kHz (AMI)

2 kHz

4 kHz

N x 8 kHz

1.544/2.048 MHz

6.48 MHz

19.44 MHz

25.92 MHz

38.88 MHz

51.84 MHz

77.76 MHz

155.52 MHz

Input

Port

Monitors

and

Selection

Control

14 x SEC

T4 DPLL/Freq. Synthesis

Digital

T4

Optional

PFD

Selector

Divider, 1/n

n = 1 to 214

Loop

Filter

DTO

T0 DPLL/Freq. Synthesis

T0

Optional

Selector

Divider, 1/n

n = 1 to 214

PFD

Digital

Loop

DTO

Filter

TCK

TDI

TMS

TRST

TDO

IEEE

1149.1

JTAG

Chip

Clock

Generator

Priority Register Set

Table

Microprocessor

Port

OCXO

Revision 3.02/November 2005 © Semtech Corp.

Page 1

T4 APLL

Frequency

Dividers

T0 APLL

(output)

Frequency

Dividers

TO APLL

(feedback)

Output

Ports

TO1

to

TO7

TO8

&

TO9

TO10

&

TO11

Outputs

T01-TO7:

E1/DS1 (2.048/

1.544 MHz)

and frequency

multiples:

1.5 x, 2 x, 3 x

4 x, 6 x, 12 x

16 x and 24 x

E3/DS3

2 kHz

8 kHz

and OC-N* rates

T08: AMI

TO9: E1/DS1

TO10: 8 kHz

(FrSync)

TO11: 2 kHz

(MFrSync)

OC-N* rates =

OC-1 51.84 MHz

OC-3 155.52 MHz

and derivatives:

6.48 MHz

19.44 MHz

25.92 MHz

38.88 MHz

51.84 MHz

77.76 MHz

155.52 MHz

311.04 MHz

F8530D_001BLOCKDIA_09

www.semtech.com