74ACT715 Ver la hoja de datos (PDF) - Fairchild Semiconductor

Número de pieza

componentes Descripción

Fabricante

74ACT715 Datasheet PDF : 14 Pages

| |||

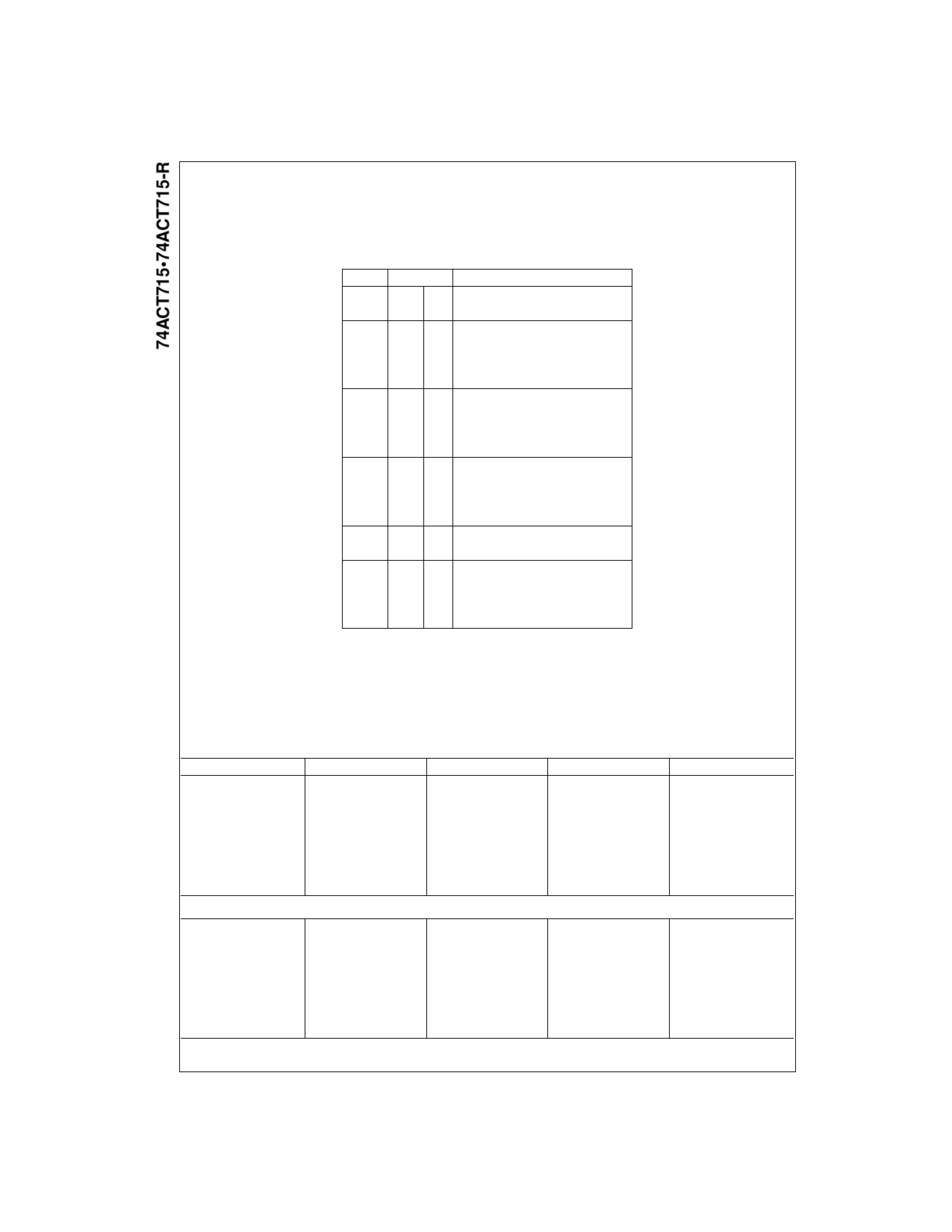

RS170 Default Register Values

The tables below show the values programmed for the

RS170 Format (using a 14.31818 MHz clock signal) and

how they compare against the actual EIA RS170 Specifica-

tions. The default signals that will be output are CSYNC,

CBLANK, HDRIVE and VDRIVE. The device initially starts

at the beginning of the odd field of interlace. All signals

have active low pulses and the clock is disabled at power

up. Registers 13 and 14 are not involved in the actual sig-

nal information. If the Vertical Interrupt was selected so that

a pulse indicating the active lines would be output.

Reg D Value H

Register Description

REG0 0 000 Status Register (715)

REG0 1024 400 Status Register (715-R)

REG1 23 017 HFP End Time

REG2 91 05B HSYNC Pulse End Time

REG3 157 09D HBLANK Pulse End Time

REG4 910 38E Total Horizontal Clocks

REG5 7 007 VFP End Time

REG6 13 00D VSYNC Pulse End Time

REG7 41 029 VBLANK Pulse End Time

REG8 525 20D Total Vertical Lines

REG9 57 039 Equalization Pulse End Time

REG10 410 19A Serration Pulse Start Time

REG11 1 001 Pulse Interval Start Time

REG12 19 013 Pulse Interval End Time

REG13 41 029 Vertical Interrupt Activate Time

REG14 526 20E Vertical Interrupt Deactivate Time

REG15 911 38F Horizontal Drive Start Time

REG16 92 05C Horizontal Drive End Time

REG17 1 001 Vertical Drive Start Time

REG18 21 015 Vertical Drive End Time

Input Clock

Line Rate

Field Rate

Frame Rate

Rate

14.31818 MHz

15.73426 kHz

59.94 Hz

29.97 Hz

Period

69.841 ns

63.556 µs

16.683 ms

33.367 ms

RS170 Horizontal Data

Signal

Width

HFP

HSYNC Width

22 Clocks

68 Clocks

HBLANK Width

156 Clocks

HDRIVE Width

HEQP Width

91 Clocks

34 Clocks

HSERR Width

68 Clocks

HPER iod

910 Clocks

RS170 Vertical Data

VFP

3 Lines

VSYNC Width

3 Lines

VBLANK Width

VDRIVE Width

20 Lines

11.0 Lines

VEQP Intrvl

VPERiod (field)

9 Lines

262.5 Lines

VPERiod (frame)

525 Lines

µs

1.536

4.749

10.895

6.356

2.375

4.749

63.556

190.67

190.67

1271.12

699.12

16.683 ms

33.367 ms

%H

7.47

17.15

10.00

3.74

7.47

100

7.62

4.20

3.63

Specification (µs)

1.5 ±0.1

4.7 ±0.1

10.9 ±0.2

0.1H ±0.005H

2.3 ±0.1

4.7 ±0.1

6 EQP Pulses

6 Serration Pulses

0.075V ± 0.005V

0.04V ± 0.006V

9 Lines/Field

16.683 ms/Field

33.367 ms/Frame

www.fairchildsemi.com

8