1417H5 Ver la hoja de datos (PDF) - Agere -> LSI Corporation

NĂșmero de pieza

componentes DescripciĂłn

Fabricante

1417H5

1417H5 Datasheet PDF : 12 Pages

| |||

Data Sheet

January 2000

NetLight 1417G5 and 1417H5-Type

ATM/SONET/SDH Transceivers with Clock Recovery

Transceiver Optical and Electrical Characteristics (continued)

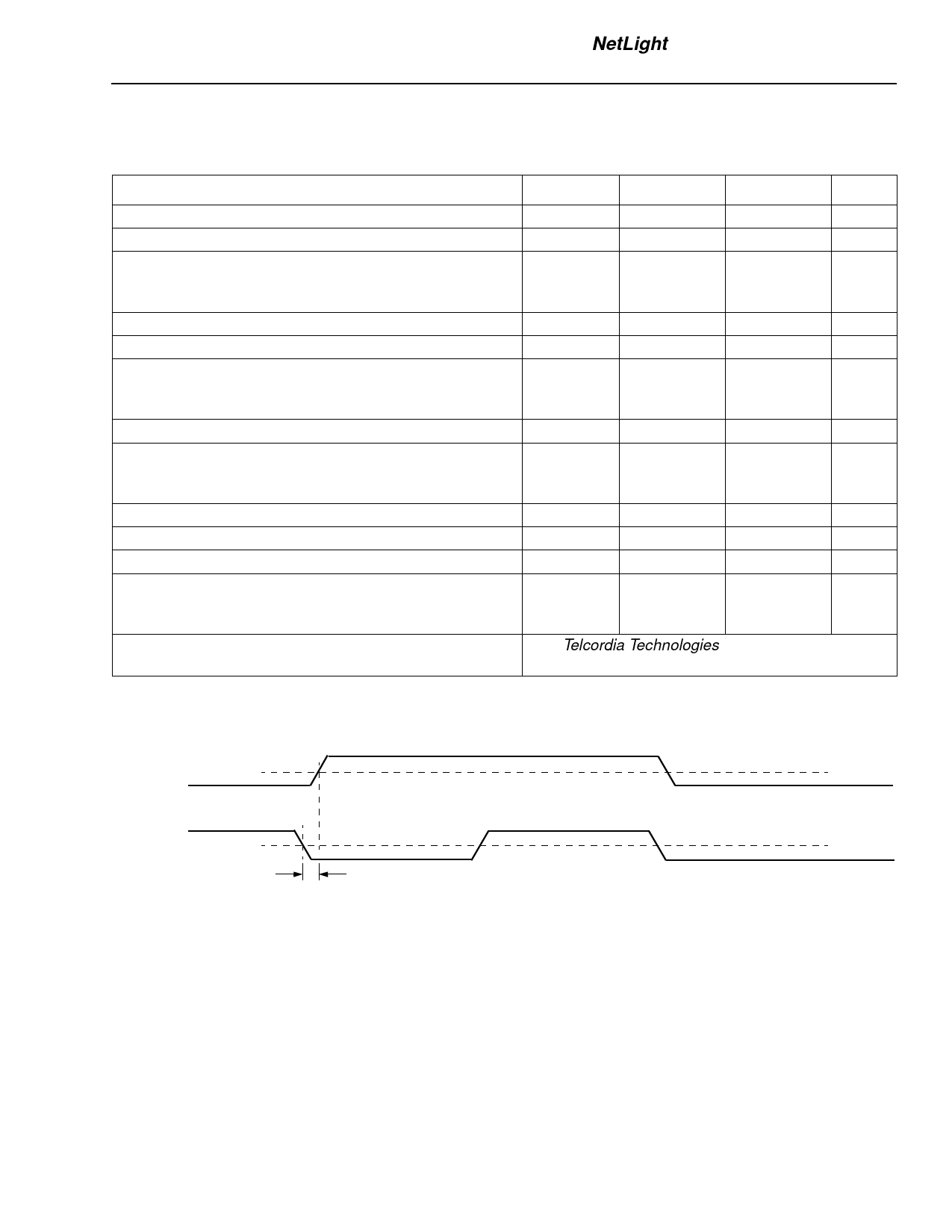

Table 3. Receiver Optical and Electrical Characteristics (TC = â40 °C to +85 °C; VCC = 3.135 V to 3.465 V)

Parameter

Symbol

Min

Max

Unit

Average Sensitivity (STM-1/STM-4)*

Maximum Input Power*

Link Status Switching Threshold:

Decreasing Light (STM-1/STM-4)

Increasing Light (STM-1/STM-4)

Link Status Hysteresis

Power Supply Current

Output Data Voltage/Clock Voltage:

Low

High

Output Data/Clock Rise and Fall Timesâ

Signal Detect Output Voltage:

Low

High

Clock Duty Cycle

Output Clock Random Jitter

Output Clock Random Jitter Peaking

Clock/Data Alignment: (See Figure 2.)

STM-1

STM-4

Jitter Tolerance/Jitter Transfer

* For 1 x 10â10 BER with an optical input using 223 â 1 PRBS.

â Typical rise and fall time is 360 ps.

PI

â

PMAX

â8

â28

dBm

â

dBm

LSTD

â45

LSTI

â45

HYS

0.5

ICCR

â

â29.0

â28.5

â

200

dBm

dBm

dB

mA

VOL

VCC â 1.81 VCC â 1.62

V

VOH

VCC â 1.025 VCC â 0.88

V

tR/tF

300

500

ps

VOL

0.0

VOH

2.4

0.8

V

VCC

V

DC

45

55

%

JC

â

0.01

UI

JP

â

0.1

dB

TCDA

â800

â200

800

ns

200

ns

Telcordia Technologies Âź GR-253-Core and

ITU-TG.958 Compliant

DATAOUT

50%

CLOCKOUT

50%

TCDA

Figure 2. Clock/Data Alignment

1-725(F).b

Agere Systems Inc.

5