V104 Ver la hoja de datos (PDF) - Integrated Circuit Systems

Número de pieza

componentes Descripción

Fabricante

V104 Datasheet PDF : 11 Pages

| |||

V104

10 BIT LVDS RECEIVER FOR VIDEO

PRELIMINARY

General Description

The V104 10 Bit LVDS Receiver for Video is designed

to support video data transmission between display

engines and video processing engines for television

and projector applications. The V104 supports up to

WXGA resolutions for Plasma, Rear Projection, Front

Projection, CRT and LCD applications.

The V104 converts the 6 LVDS (Low Voltage

Differential Signaling) video data stream pairs to 35

CMOS/TTL data bits with a rising or falling edge clock.

The clock edge selection is performed using a

dedicated pin.

In conjunction with the V103 transmitter, the V104 can

transmit 10 bits per color (R, G, B) along with 5 bits of

control and timing data (HSYNC, VSYNC, DE, CNTL1,

CNTL2) over a low EMI, low bus width connection

including connectors and standard LVDS cabling.

Features

• Pin & function compatible with the THC63LVD104A

• Wide pixel clock range: 8 - 90 MHz

• Supports resolutions from 480p to WXGA

• Internal PLL does not require external loop filter

• Clock edge selection for TTL alignment selectable

• Power down mode

• Single 3.3V supply

• Low power consumption CMOS design

• 64-pin TQFP lead free package

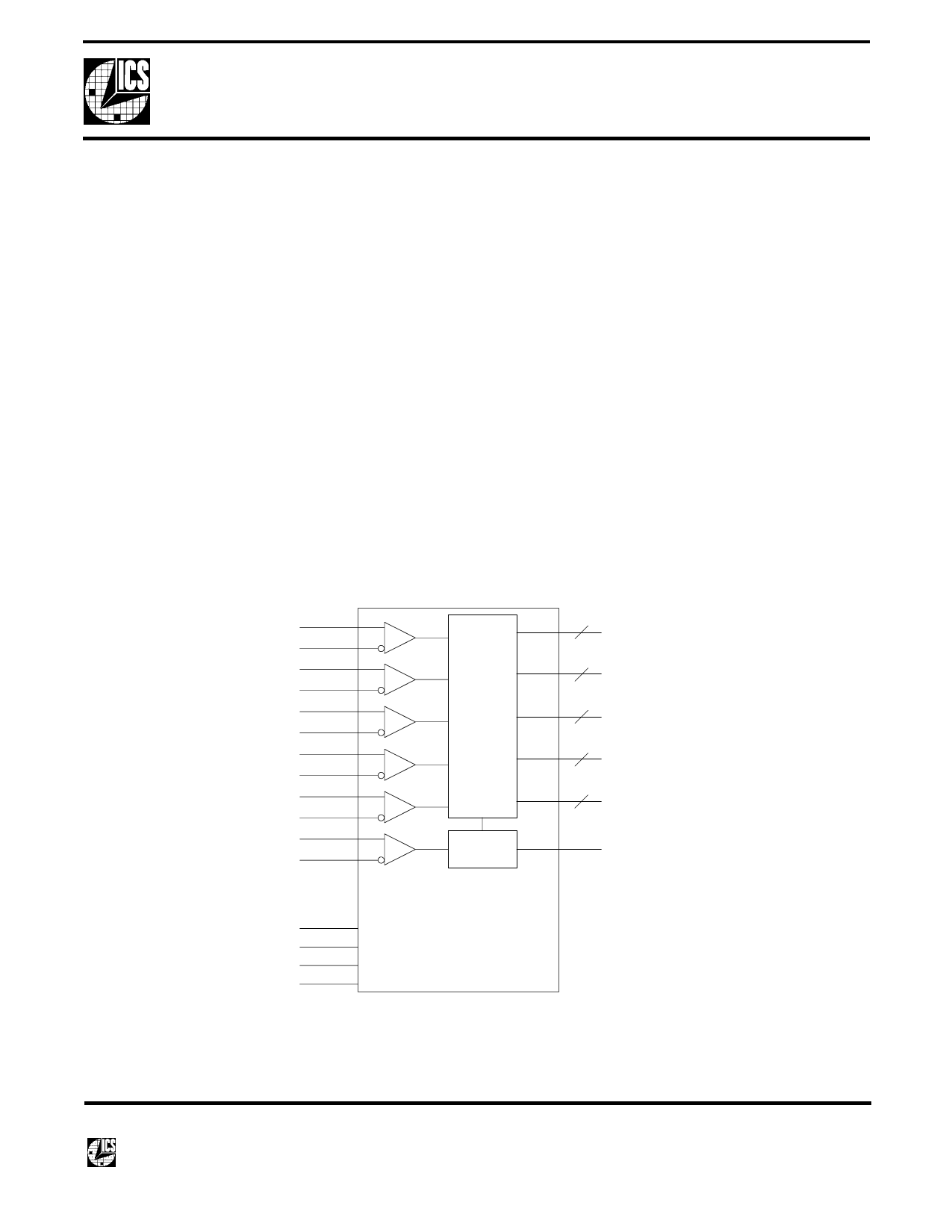

Block Diagram

LVDS Input

RA+/-

RB+/-

RC+/-

RD+/-

RE+/-

RCLK+/-

(8 to 90 MHz)

CMOS/TTL Input

TEST

PD

OE

R/F

Serial to

Parallel

PLL

CMOS/TTL Output

7 RA6-RA0

7 RB6-RB0

7 RC6-RC0

7 RD6-RD0

7 RE6-RE0

CLKOUT

V104 Datasheet

1

1/12/05

Revision 1.6

Integrated Circuit Systems • 525 Race Street, San Jose, CA 95126 • tel (408) 297-1201 • www.icst.com