TDA18271HD Ver la hoja de datos (PDF) - NXP Semiconductors.

Número de pieza

componentes Descripción

Fabricante

TDA18271HD Datasheet PDF : 70 Pages

| |||

NXP Semiconductors

TDA18271HD

Silicon Tuner IC

9.3.4 Description of power level byte (read mode)

There are 9 power level bits sent in power level bytes 2 and 3. They indicate the

composite voltage gain of the LNA, the loaded attenuator voltage gains, and the level at

the input of the RF AGC.

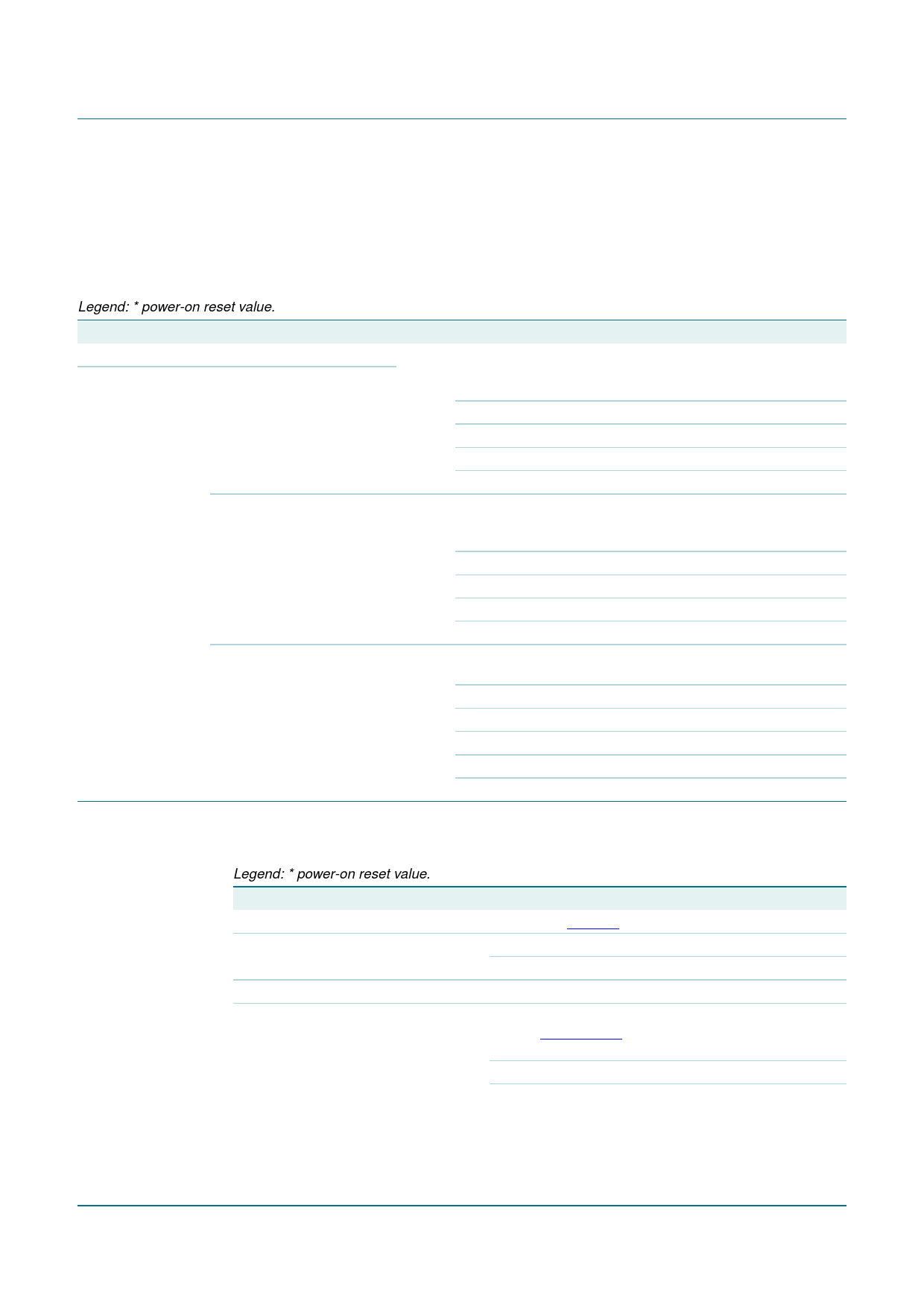

Table 12. PL - Power level (address 02h and 03h) bit description

Legend: * power-on reset value.

Address Register Bit Symbol

Access Value Description

03h

EP1

7

POWER_LEVEL[8] R

02h

PL

7

POWER_LEVEL[7]

AGC2 gain, attenuator voltage gain including load,

the attenuator load is 50 Ω (allows the maximum gain

of −6 dB)

00

−15 dB

01

−12 dB

10

−9 dB

11

−6 dB

6 to 5 POWER_LEVEL[6:5] R

AGC1 gain, LNA voltage gain, the LNA voltage gain

assumes a 75 Ω source impedance and a low output

impedance

00

6 dB

01

9 dB

10

12 dB

11

15 dB

4 to 0 POWER_LEVEL[4:0] R

sensed level at the input of the RF AGC, detector

slope is −1 dB/step

0 0000 103 dBµV (RMS value)

0 0001 102 dBµV (RMS value)

...

...

1 1110 73 dBµV (RMS value)

1 1111 72 dBµV (RMS value)

9.3.5 Description of Easy prog byte 1

Table 13. EP1 - Easy prog byte 1 (subaddress 03h) bit description

Legend: * power-on reset value.

Bit Symbol

Access Value Description

7

POWER_LEVEL[8] R

see Table 12

6

DIS_POWER_LEVEL R/W 1* power level disabled

0

power level enabled

5

-

R/W 0* must be set to 0

4

RF_CAL_OK

R/W

RF tracking filter calibration procedure (see

Section 9.4.9); updated each time the procedure

is started

1

successful

0*

not successful

TDA18271HD_4

Product data sheet

Rev. 04 — 19 May 2009

© NXP B.V. 2009. All rights reserved.

15 of 70