UPC4061G2 Ver la hoja de datos (PDF) - NEC => Renesas Technology

Número de pieza

componentes Descripción

Fabricante

UPC4061G2 Datasheet PDF : 12 Pages

| |||

µPC4061

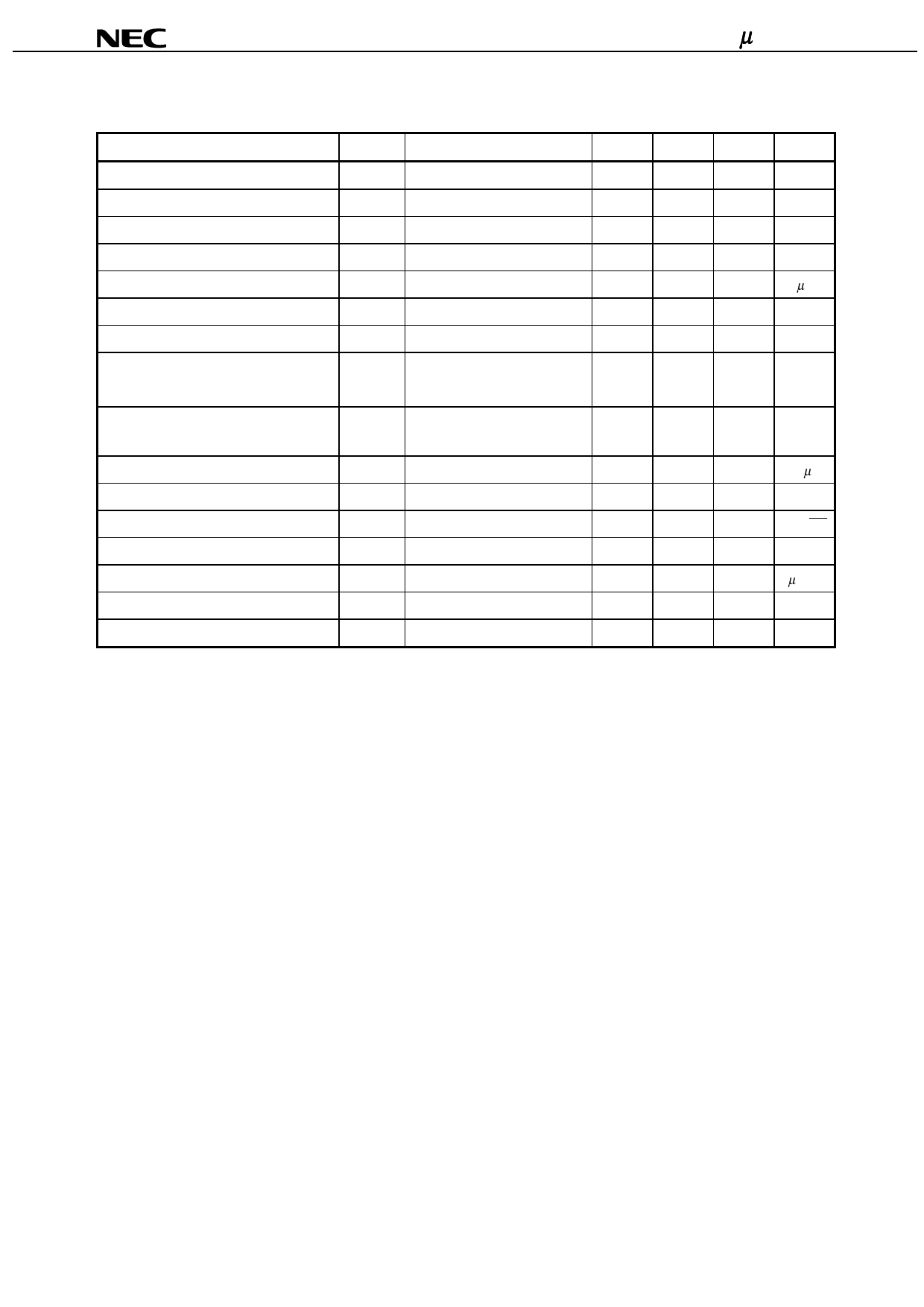

ELECTRICAL CHARACTERISTICS (TA = 25 °C, V± = ±15 V)

Parameter

Input Offset Voltage

Input Offset Current Note 7

Input Bias Current Note 7

Large Signal Voltage Gain

Supply Current

Common Mode Rejection Ratio

Supply Voltage Rejection Ratio

Output Voltage Swing

Symbol

Conditions

VIO

RS ≤ 50 Ω

IIO

IB

AV

RL ≥ 10 kΩ , VO = ±10 V

ICC

IO = 0 A

CMR

SVR

Vom

RL ≥ 10 kΩ

MIN.

3000

70

70

±12

Common Model Input Voltage Range

VICM

±12

Slew Rate

Unity Gain Frequency

Input Equivalent Noise Voltage Density

Input Offset Voltage

Average VIO Temperature Drift

Input Offset CurrentNote 7

Input Bias CurrentNote 7

SR

funity

en

VIO

∆VIO/∆T

IIO

IB

AV = 1

RS = 100 Ω, f = 1 kHz

RS ≤ 50 Ω, TA = –20 to +70 °C

TA = –20 to +70 °C

TA = –20 to +70 °C

TA = –20 to +70 °C

TYP.

±2

±5

10

9000

220

90

90

+14.0

–13.6

+15

–13

3

1

30

±10

MAX.

Unit

±10

mV

±50

pA

100

pA

250

µA

dB

dB

V

V

V/µs

MHz

nV/√Hz

±15

mV

µV/°C

±2

nA

3.5

nA

Notes 7. Input bias currents flow into IC. Because each currents are gate leak current of P-channel J-FET on input

stage. And that are temperature sensitive. Short time measuring method is recommendable to maintain the

junction temperature close to the operating ambient temperature.

Data Sheet G15038EJ3V0DS00

3