PF28F1602C3TD70 Ver la hoja de datos (PDF) - Intel

NÚmero de pieza

componentes DescripciÃģn

Fabricante

PF28F1602C3TD70 Datasheet PDF : 75 Pages

| |||

C3 SCSP Flash Memory

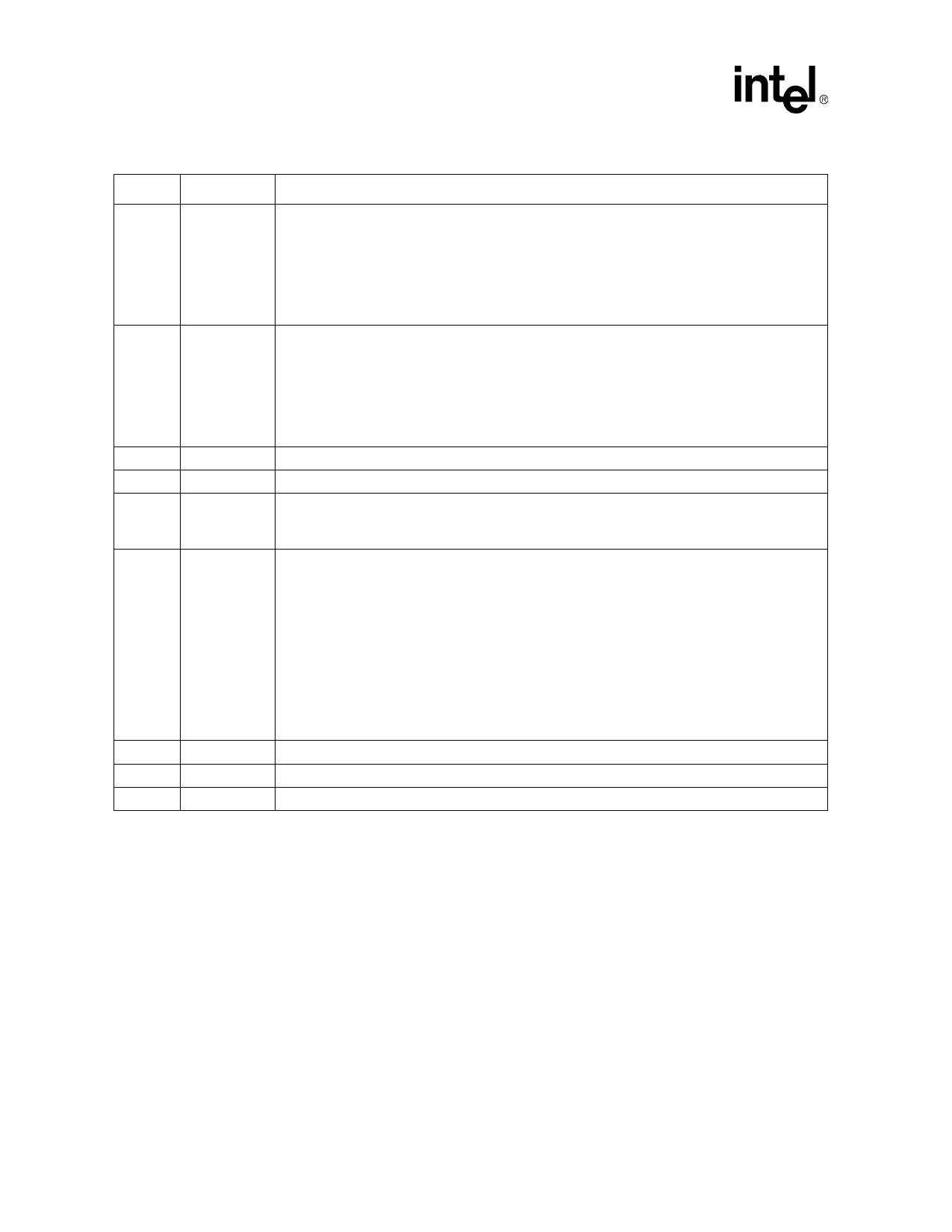

Table 2.

Symbol

F-RP#

F-WP#

F-VCC

F-VCCQ

S-VCC

F-VPP

F-VSS

S-VSS

NC

IntelÂŪ Advanced+ Boot Block SCSP Ball Descriptions (Sheet 2 of 2)

Type

INPUT

INPUT

SUPPLY

SUPPLY

SUPPLY

INPUT /

SUPPLY

SUPPLY

SUPPLY

Name and Function

FLASH RESET/DEEP POWER-DOWN: Uses two voltage levels (VIL, VIH) to control reset/deep

power-down mode.

âĒ When F-RP# is at logic low, the device is in reset/deep power-down mode, which drives

the outputs to High-Z, resets the Write State Machine, and minimizes current levels (ICCD).

âĒ When F-RP# is at logic high, the device is in standard operation.

âĒ When F-RP# transitions from logic-low to logic-high, the device resets all blocks to locked and

defaults to the read array mode.

FLASH WRITE PROTECT: Controls the lock-down function of the flexible Locking feature.

âĒ When F-WP# is a logic low, the lock-down mechanism is enabled and blocks marked

lock-down cannot be unlocked through software. After F-WP# goes low, any blocks previously

marked lock-down revert to that state.

âĒ When F-WP# is logic high, the lock-down mechanism is disabled. Blocks previously

locked-down are now locked, and can be unlocked or locked through software.

See Section 7.0, âSystem Design Considerationsâ on page 41 for details on block locking.

FLASH POWER SUPPLY: [2.7 Vâ3.3 V] Supplies power for device core operations.

FLASH I/O POWER SUPPLY: [2.7 Vâ3.3 V] Supplies power for device I/O operations.

SRAM POWER SUPPLY: [2.7 Vâ3.3 V] Supplies power for device operations.

See Section 7.2.2, âF-VCC, F-VPP and F-RP# Transitionâ on page 42 for details of power

connections.

FLASH PROGRAM/ERASE POWER SUPPLY: [1.65 Vâ3.3 V or 11.4 Vâ12.6 V] Operates as an

input at logic levels to control complete flash memory protection. Supplies power for accelerated

flash memory program and erase operations in 12 V Âą 5% range. This ball cannot be left floating.

Lower F-VPP âĪ VPPLK, to protect all contents against Program and Erase commands.

Set F-VPP = F-VCC for in-system read, program and erase operations. In this configuration,

F-VPP can drop as low as 1.65 V to allow for resistor or diode drop from the system supply.

Note: If F-VPP is driven by a logic signal, then VIH = 1.65 V. That is, F-VPP must remain above

1.65 V to modify in-system flash memory.

Raise F-VPP to 12 V Âą 5% for faster program and erase in a production environment. 12 V Âą

5% to F-VPP can be applied for a maximum of 1000 cycles on the main blocks and 2500 cycles on

the parameter blocks. F-VPP can be connected to 12 V for a total of 80 hours maximum.

FLASH GROUND: For all internal circuitry. All ground inputs must be connected.

SRAM GROUND: For all internal circuitry. All ground inputs must be connected.

NOT CONNECTED: Internally disconnected within the device.

26 Aug 2005

10

IntelÂŪ Advanced+ Boot Block Flash Memory (C3) SCSP Family

Order Number: 252636, Revision: 004

Datasheet