RA8835A Ver la hoja de datos (PDF) - RAIO

Número de pieza

componentes Descripción

Fabricante

RA8835A Datasheet PDF : 6 Pages

| |||

Preliminary Version 1.0

RA8835A

Dot Matrix LCD Controller

VCE

Display Memory Chip Select.

Active-LOW static memory standby control signal. VCE can be used with CS .

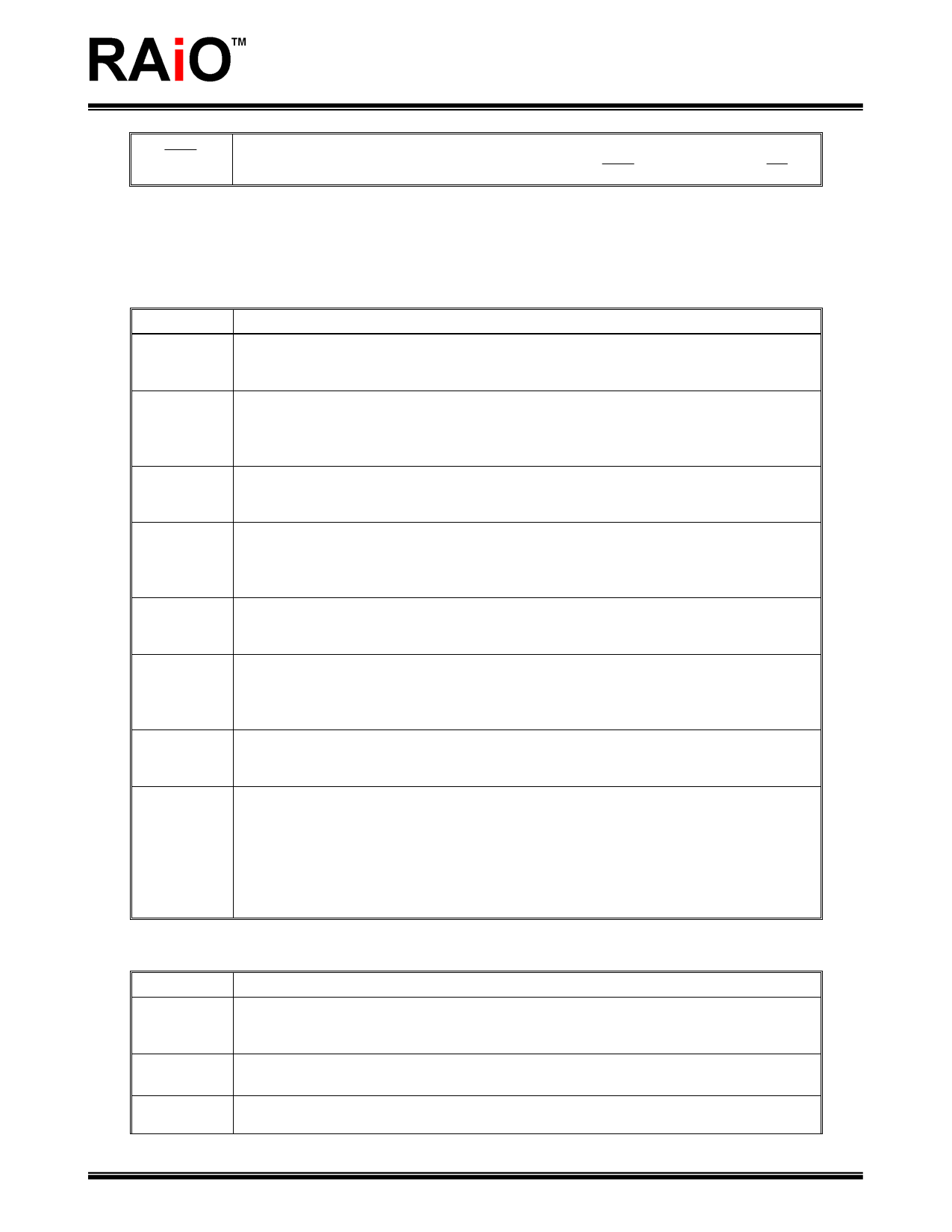

5.1.3 LCD Drive Signals

In order to provide effective low-power drive for LCD matrixes, the RA8835A series can directly

control both the X- and Y-drivers using an enable chain.

Pin Name

XD0 to XD3

XSCL

XECL

LP

WF

YSCL

YD

YDIS

Function

Data Output for Driver.

4-bit X-driver (column drive) data outputs. Connect these outputs to the inputs

of the X-driver chips.

Latch Clock.

The falling edge of XSCL latches the data on XD0 to XD3 into the input shift

registers of the X-drivers. To conserve power, this clock halts between LP and

the start of the following display line (See section 6.3.7).

Trigger Clock for Chain Cascade.

The falling edge of XECL triggers the enable chain cascade for the X-drivers.

Every 16th clock pulse is output to the next X-driver.

Latch Pulse.

LP latches the signal in the X-driver shift registers into the output data latches.

LP is a falling-edge triggered signal, and pulses once every display line.

Connect LP to the Y-driver shift clock on modules.

AC Drive Output.

The WF period is selected to be one of two values with SYSTEM SET

command.

Latch Clock for YD.

The falling edge of YSCL latches the data on YD into the input shift registers of

the Y-drivers. YSCL is not used with driver ICs which use LP as the Y-driver

shift clock.

Data Pulse Output for Y Drivers.

It is active during the last line of each frame, and is shifted through the Y drivers

one by one (by YSCL), to scan the display’s common connections.

Power-down Output Signal.

YDIS is HIGH while the display drive outputs are active. YDIS goes LOW one or

two frames after the sleep command is written to the RA8835A series. All Y-

driver outputs are forced to an intermediate level (de-selecting the display

segments) to blank the display. In order to implement power-down operation in

the LCD unit, the LCD power drive supplies must also be disabled when the

display is disabled by YDIS.

5.1.4. Oscillator and Power

Pin Name

XG

XD

VDD

Function

Crystal Connection for Internal Oscillator

This pin can be driven by an external clock source that satisfies the timing

specifications of the EXT f0 signal (See section 7.3.6).

Crystal Connection for Internal Oscillator

Leave this pin open when using an external clock source.

2.7 to 5.5V Supply.

This may be the same supply as the controlling microprocessor.

RAiO TECHNOLOGY INC.

5/6

www.raio.com.tw