MAX7310 Ver la hoja de datos (PDF) - Maxim Integrated

Número de pieza

componentes Descripción

Fabricante

MAX7310 Datasheet PDF : 15 Pages

| |||

2-Wire-Interfaced 8-Bit I/O Port Expander

with Reset

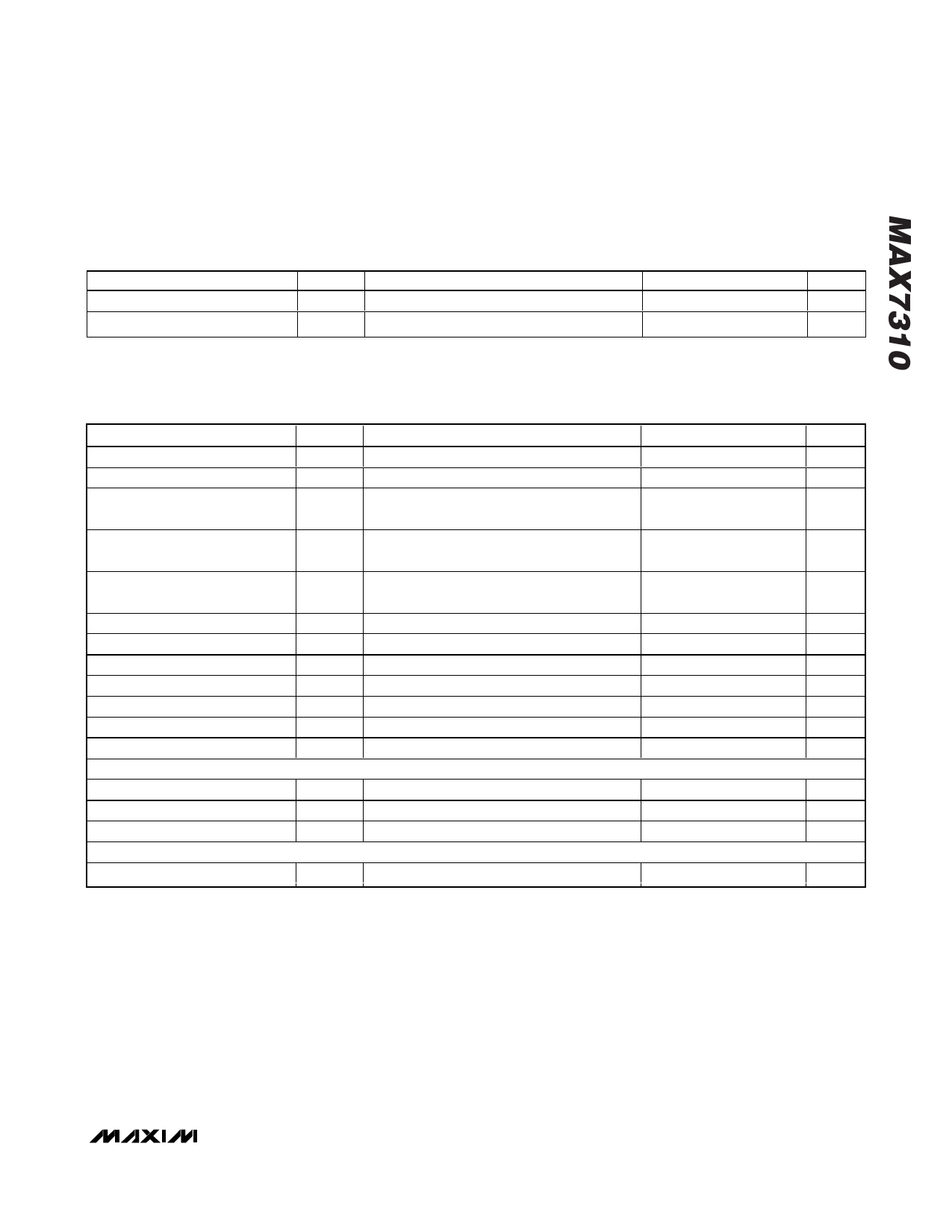

DC ELECTRICAL CHARACTERISTICS (continued)

(V+ = 2.3V to 5.5V, GND = 0, RESET = V+, TA = -40°C to +125°C, unless otherwise noted. Typical values are at V+ = 3.3V, TA = +25°C.)

(Note 1)

PARAMETER

Leakage Current

Input Capacitance

SYMBOL

CONDITIONS

MIN TYP MAX UNITS

-1

+1

µA

10

pF

AC ELECTRICAL CHARACTERISTICS

(V+ = 2.3V to 5.5V, GND = 0, RESET = V+, TA = -40°C to +125°C, unless otherwise noted.) (Note 1)

PARAMETER

SYMBOL

CONDITIONS

MIN

SCL Clock Frequency

fSCL (Note 2)

BUS Timeout

tTIMEOUT

30

Bus Free Time Between STOP

and START Condition

tBUF Figure 2

1.3

Hold Time (Repeated) START

Condition

tHD, STA Figure 2

0.6

Repeated START Condition Setup

Time

tSU, STA

Figure 2

0.6

STOP Condition Setup Time

tSU, STO Figure 2

0.6

Data Hold Time

tHD, DAT Figure 2 (Note 3)

Data Setup Time

tSU, DAT Figure 2

0.1

SCL Low Period

tLOW Figure 2

1.3

SCL High Period

tHIGH Figure 2

0.7

SCL/SDA Fall Time (Transmitting)

Pulse Width of Spike Supressed

PORT TIMING

tF

Figure 2 (Note 4)

tSP (Note 5)

Output Data Valid

tPV Figure 9

Input Data Setup Time

tPS Figure 10

29

Input Data Hold Time

tPH Figure 10

0

RESET

Reset Pulse Width

100

TYP MAX UNITS

400

kHz

60

ms

µs

µs

µs

µs

0.9

µs

µs

µs

µs

250

ns

50

ns

1

µs

µs

µs

ns

Note 1: All parameters are 100% production tested at TA = +25°C. Specifications over temperature are guaranteed by design.

Note 2: Minimum SCL clock frequency is limited by the MAX7310 bus timeout feature, which resets the serial bus interface if either

SDA or SCL is held low for a 30ms minimum.

Note 3: A master device must internally provide a hold time of at least 300ns for the SDA signal (referred to the VIL of the SCL signal) in

order to bridge the undefined region of SCL’s falling edge.

Note 4: tF measured between 90% to 10% of V+.

Note 5: Input filters on the SDA and SCL inputs suppress noise spikes less than 50ns.

_______________________________________________________________________________________ 3