IS25C01 Ver la hoja de datos (PDF) - Integrated Silicon Solution

Número de pieza

componentes Descripción

Fabricante

IS25C01 Datasheet PDF : 17 Pages

| |||

IS25C01

ISSI ®

DEVICE OPERATION

The operations of the IS25C01 is controlled by a set of instructions that are clocked-in serially SI pin. (See Table 3). To

begin an instruction, the chip select (CS) should be dropped Low. Subsequently, each Low-to-High transition of the

clock (SK) will latch a stable value on the SI pin. After the 8-bit op-code, it may be appropriate to continue to input an

address or data to SI, or to output data from SO. During data output, values appear on the falling edge of SK. All bits

are transferred with MSB first. Upon the last bit of communication, but prior to any following Low-to-High transition of

SK, CS should be raised High to end the transaction. The device then would enter Standby Mode if no internal pro-

gramming were underway.

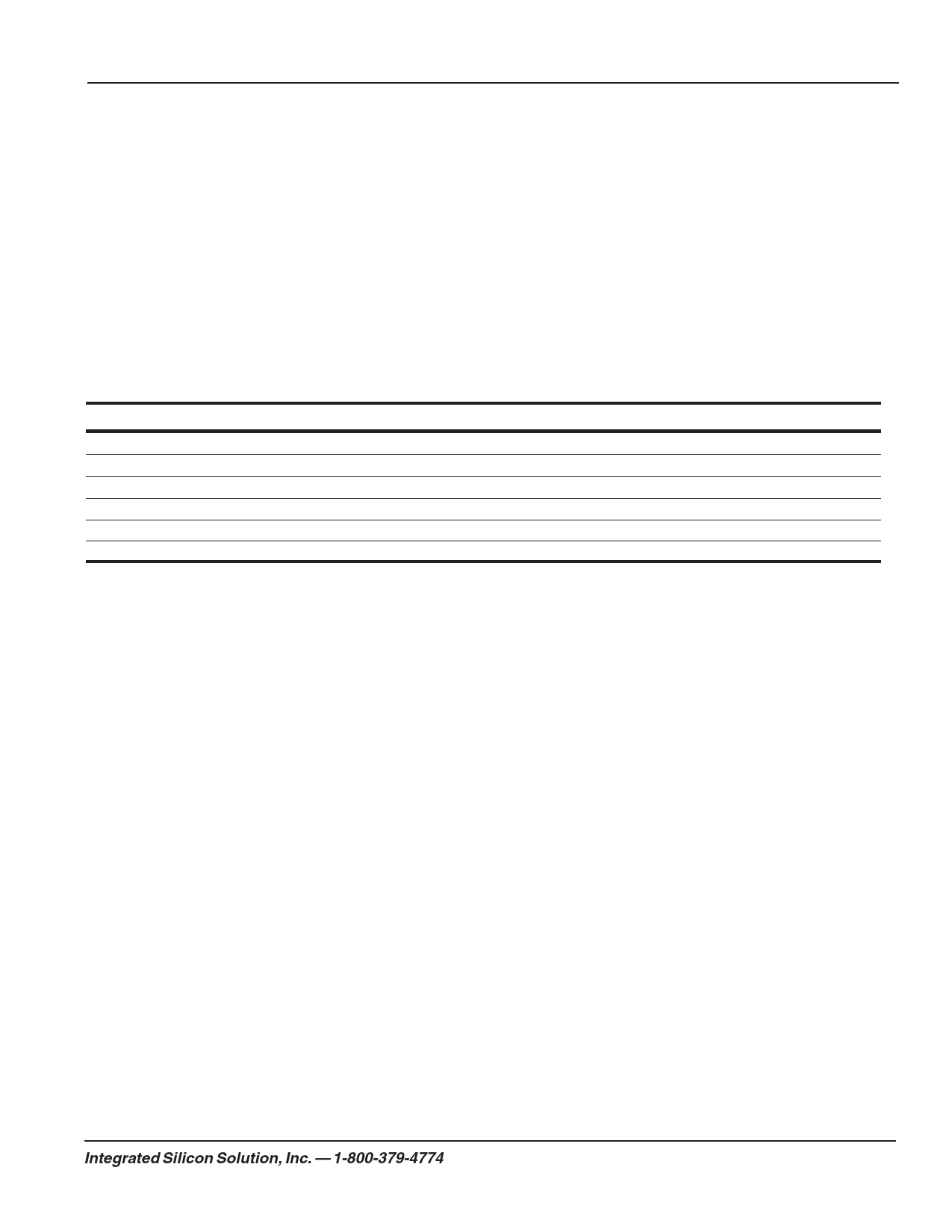

Table 3. Instruction Set

Name Op-code

Operation

Address

Data(SI)

Data (SO)

WREN 0000 X110

WRDI 0000 X100

RDSR 0000 X101

WRSR 0000 X001

READ 0000 X011

WRITE 0000 X010

Set Write Enable Latch

Reset Write Enable Latch

Read Status Register

Write Status Register

Read Data from Array

Write Data to Array

-

-

-

-

A7-A0

A7-A0

-

-

-

D7-D0

-

D7-D0,...

-

-

D7-D0,...

-

D7-D0,...

-

1. X = Don’t care bit. For consistency, it is best to use “0”.

2. A = X.

7

3. If the bits clocked-in for an op-code are invalid, SO remains high impedance, and upon CS going High there is no

affect. A valid op-code with an invalid number of bits clocked-in for address or data will cause an attempt to modify the

array or Status Register to be ignored.

WRITE ENABLE (WREN)

When Vcc is initially applied, the device powers up with

both status register and entire array in a write-disabled

state. Upon completion of Write Disable (WRDI), Write

Status Register (WRSR), or Write Data to Array

(WRITE), the device resets the WEN bit in the Status

Register to 0. Prior to any data modification, a WREN

instruction is necessary to set WEN to 1. (See Figure 2

for timing).

WRITE DISABLE (WRDI)

The device can be completely protected from modifica-

tion by resetting WEN to 0 through the WRDI instruc-

tion. (See Figure 3 for timing).

READ STATUS REGISTER (RDSR)

The Read Status instruction indicates the status of the

Block Protection setting (see Table 2), the Write Enable

state, and the RDY status. RDSR is the only instruction

accepted when a write cycle is underway. It is recom-

mended that the status of RDY be checked, especially

prior to an attempted modification of data. The 8 bits of

the Status Register can be repeatedly output on SO

after the initial Op-code. (See Figure 4 for timing).

Integrated Silicon Solution, Inc. — 1-800-379-4774

5

Preliminary Information Rev. 00B

12/23/05