AK4309 Ver la hoja de datos (PDF) - Asahi Kasei Microdevices

Número de pieza

componentes Descripción

Fabricante

AK4309 Datasheet PDF : 14 Pages

| |||

ASAHI KASEI

Zero detection

[AK4309B]

When the input data at both channels are continuously zeros for 8192 LRCK cycles, DZF goes to "H". DZF

immediately goes "L" if input data are not zero after going DZF "H".

System Reset

The AK4309B should be reset once by bringing RST "L" upon power-up. The AK4309B is powered up and the

internal timing starts clocking by LRCK "↑" after exiting reset and power down state by MCLK. The AK4309B is

in power-down mode until LRCK is input.

SYSTEM DESIGN

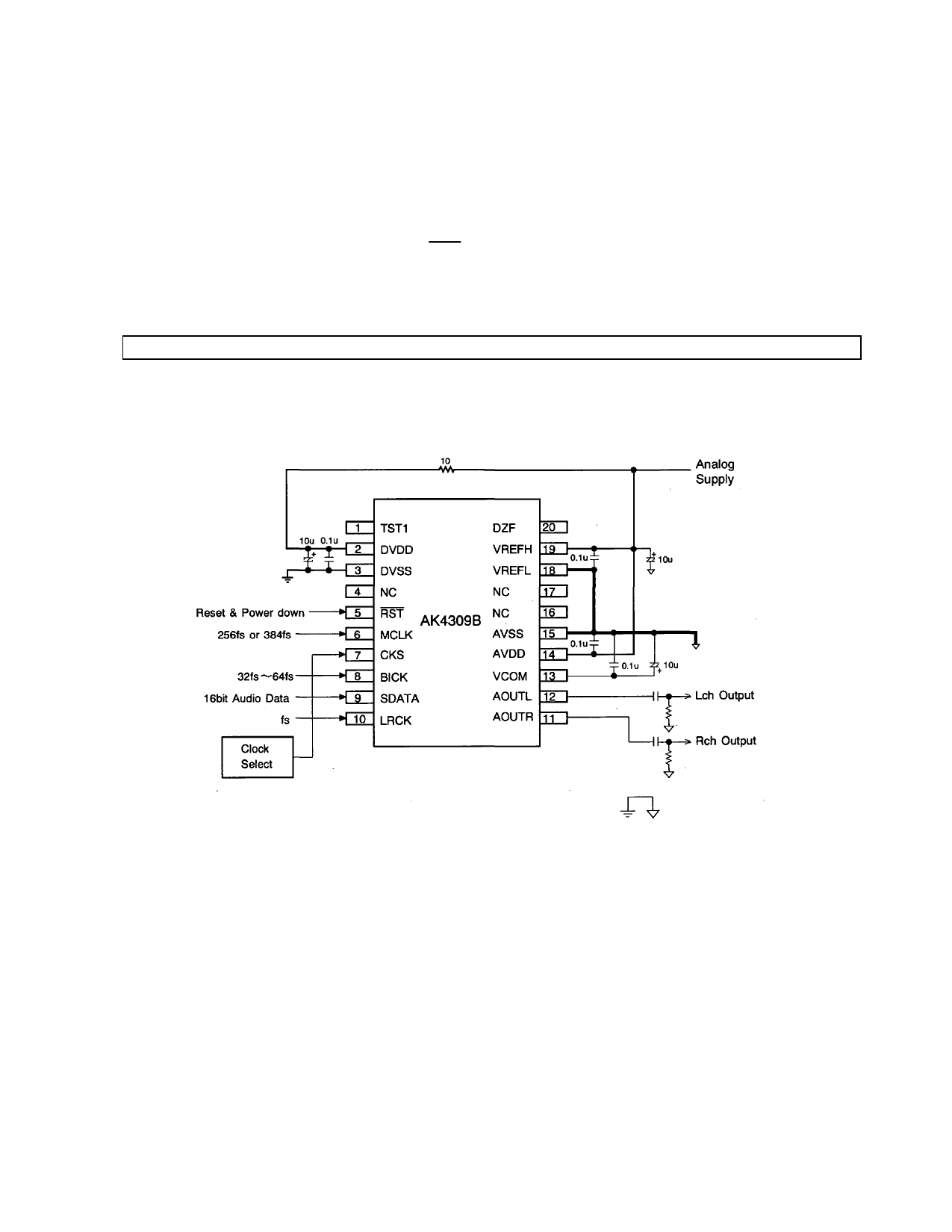

Figure 3 shows the system connection diagram. An evaluation board[AKD4310] is available which

demonstrates the optimum layout, power supply arrangements and measurement results.

Figure 3 . Typical Connection Diagram

Notes:

- LRCK=fs, BICK≥32fs, MCLK=256fs at CKS="L", MCLK=384fs at CKS="H".

- Power lines of AVDD and DVDD should be distributed separately from the point

with low impedance of regulator etc.

- When AOUT drives some capacitive load, some resistor should be added

in series between AOUT and capacitive load.

- The capacitor value on VCOM depends on low frequency noise level of power supply.

0177-E-00

- 10 -

1997/6