SL34118D Ver la hoja de datos (PDF) - System Logic Semiconductor

Número de pieza

componentes Descripción

Fabricante

SL34118D Datasheet PDF : 12 Pages

| |||

SL34118

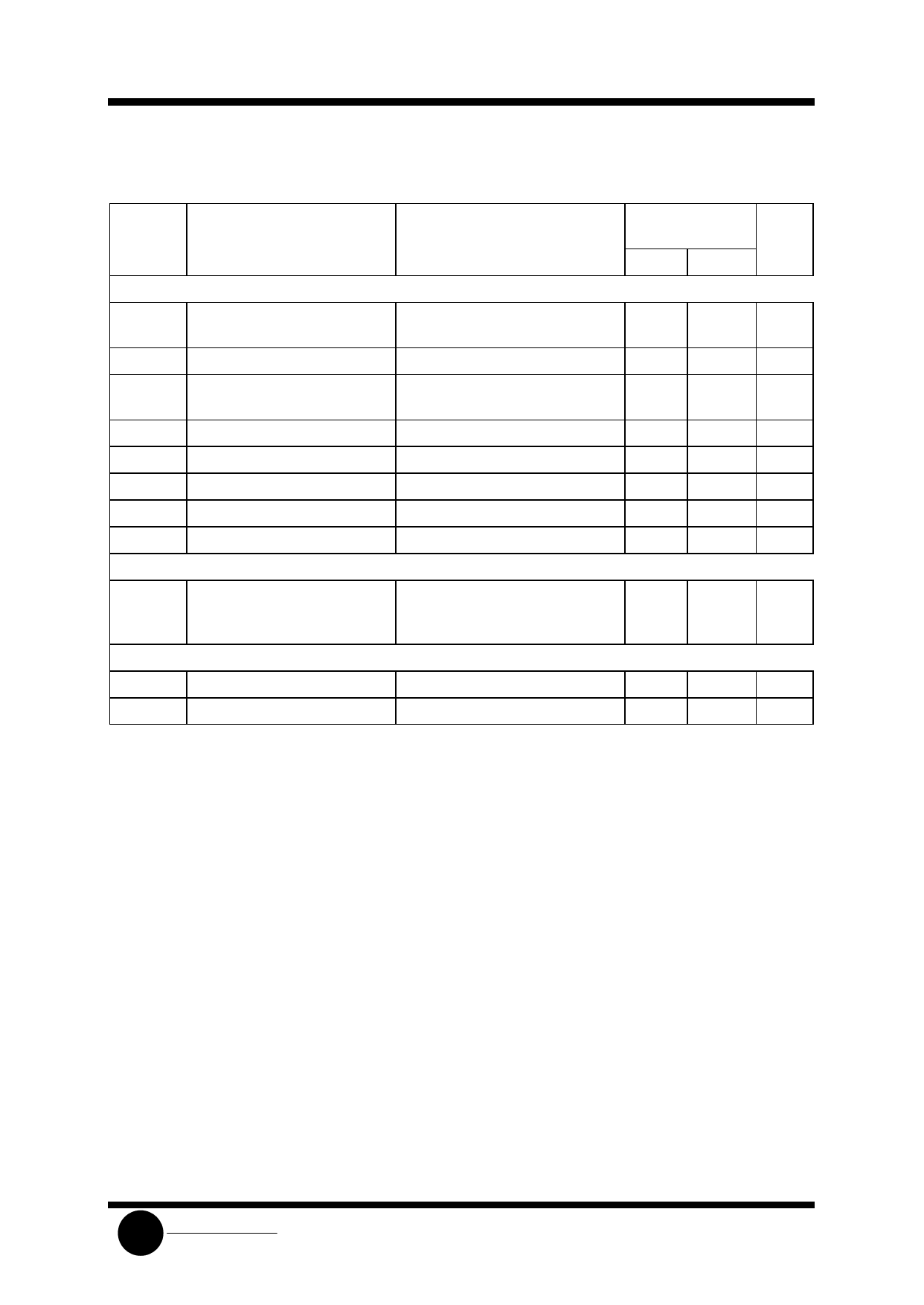

ELECTRICAL CHARACTERISTICS(TA = -25 to +70°C, VCC = 5.0 V , CD = 0.8 V, unless noted)

Guaranteed

Symbol

Parameter

Test Conditions

Limits

Unit

Min Max

HYBRID AMPLIFIERS

HVOS HTO - Offset

VHTO- - VB,

Freedback R= 51 KΩ

VB - 25 VB +25 mV

HBVOS HTO - to HTO+ Offset

Freedback R= 51 KΩ

VB - 37 VB +37 mV

AVOLH Open Loop Gain

HTI to HTO-, f = 100 Hz,

VHTI = 20 mV

57

-

dB

AVCLH Closed Loop Gain

HTO- to HTO+

-2.8

2.2

dB

VHT-H HTO- High Voltage

IOUT=-5.0 mA, VHTI=VB -1.0 V

2.8

-

V

VHT-L HTO- Low Voltage

IOUT=5.0 mA, VHTI=VB +1.5 V

-

375

mV

VHT+H HTO+ High Voltage

IOUT=-5.0 mA,VHTI=VB +1.5 V

2.8

-

V

VHT+L HTO+ Low Voltage

IOUT=5.0 mA, VHTI=VB -1.0 V

-

562

mV

LEVEL DETECTORS AND BACKGROUND NOISE MONITORS

ITH* Transmit-Recieve Switching Ratio of Current at RLI1 + RLI2 to 0.8

1.2

Threshold

20 µA at TLI1 + TLI2 to switch

from Tx to Rx

FILTER

FOVOS

IFO

Voltage Offset at FO

FO Sink Current

VFO -VB, 220 KΩ from VB to FI

VB = VFO, VFI = 0 V

VB-250 VB +25 mV

112

500

µA

Note. 1. All currents into a device pin are positive, those out of a pin are negative. Algebraic convention rather

than magnitude is used to define limits.

* @25°C

SLS

System Logic

Semiconductor