UPD16732AN-XXX Ver la hoja de datos (PDF) - NEC => Renesas Technology

Número de pieza

componentes Descripción

Fabricante

UPD16732AN-XXX

UPD16732AN-XXX Datasheet PDF : 24 Pages

| |||

µ PD16732A, 16732B

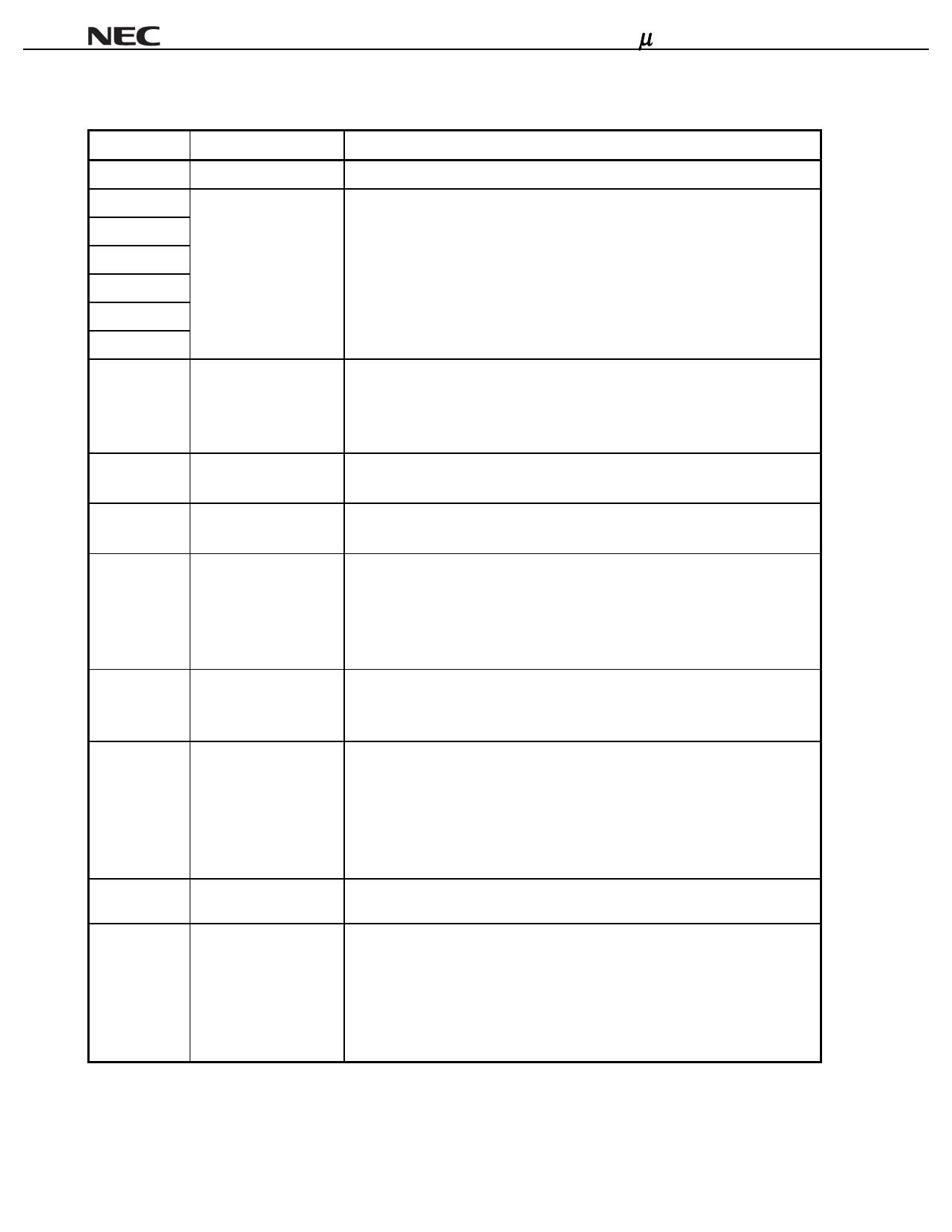

4. PIN FUNCTIONS

Pin Symbol

Pin Name

Description

(1/2)

S1 to S384

Driver output

The D/A converted 64-gray-scale analog voltage is output.

D00 to D05

D10 to D15

D20 to D25

Display data input

The display data is input with a width of 36 bits, viz., the gray scale data (6 bits)

by 6 dots (2 pixels).

DX0: LSB, DX5: MSB

D30 to D35

D40 to D45

D50 to D55

R,/L

Shift direction control

These refer to the start pulse input/output pins when driver ICs are connected in

input

cascade. The shift directions of the shift registers are as follows.

R,/L = H : STHR input, S1 → S384, STHL output

R,/L = L : STHL input, S384 → S1, STHR output

STHR

Right shift start pulse

input/output

R,/L = H : Becomes the start pulse input pin.

R,/L = L : Becomes the start pulse output pin.

STHL

Left shift start pulse

input/output

R,/L = H : Becomes the start pulse output pin.

R,/L = L : Becomes the start pulse input pin.

CLK

Shift clock input

Refers to the shift register’s shift clock input. The display data is incorporated into

the data register at the rising edge.

At the rising edge of the 64th clock after the start pulse input, the start pulse

output reaches the high level, thus becoming the start pulse of the next-level

driver.

STB

Latch input

The contents of the data register are transferred to the latch circuit at the rising

edge. And, at the falling edge, the gray scale voltage is supplied to the driver. It

is necessary to ensure input of one pulse per horizontal period.

POL

POL2

LPC

•

Polarity input

Data inversion

Low power control input

POL = L : The S2n–1 output uses V0 to V4 as the reference supply. The S2n output

uses V5 to V9 as the reference supply.

POL = H: The S2n–1 output uses V5 to V9 as the reference supply. The S2n output

uses V0 to V4 as the reference supply.

S2n-1 indicates the odd output: and S2n indicates the even output. Input of the POL

signal is allowed the setup time (tPOL-STB) with respect to STB’s rising edge.

POL2 = H : Display data is inverted.

POL2 = L : Display data is not inverted

The current consumption is lowered by controlling the constant current source of

the output amplifier. In low power mode (LPC = “L”), the VDD2 of static current

consumption can be reduced to two thirds of the normal current consumption. This

pin is pulled up to the VDD1 power supply inside the IC.

LPC = H or Open : Normal power mode

LPC = L : Low power mode

4

Data Sheet S13972EJ3V0DS00