TE28F400B3T110 Ver la hoja de datos (PDF) - Intel

Número de pieza

componentes Descripción

Fabricante

TE28F400B3T110 Datasheet PDF : 48 Pages

| |||

SMART 3 ADVANCED BOOT BLOCK

E

Number

-001

-002

-003

-004

-005

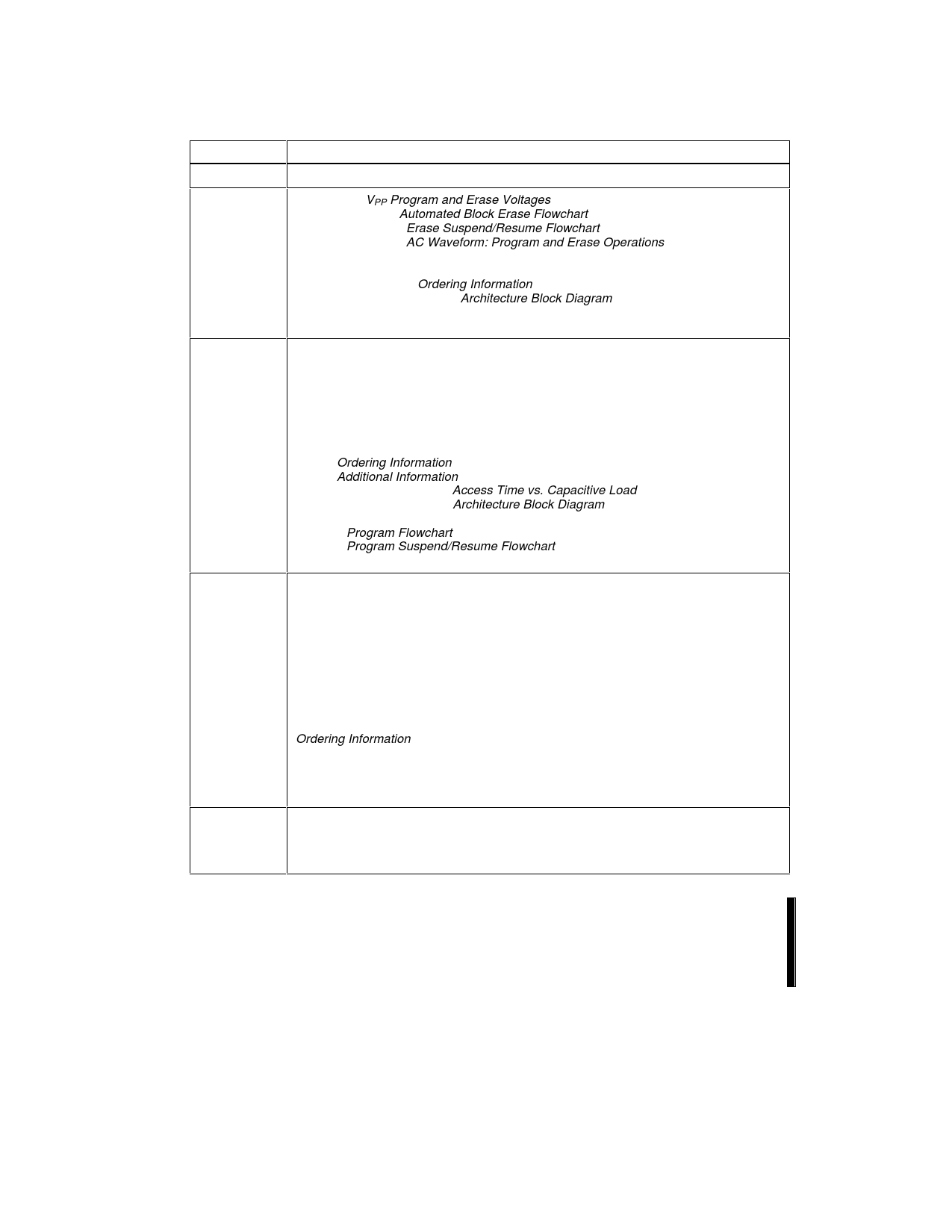

REVISION HISTORY

Description

Original version

Section 3.4, VPP Program and Erase Voltages, added

Updated Figure 9: Automated Block Erase Flowchart

Updated Figure 10: Erase Suspend/Resume Flowchart (added program to table)

Updated Figure 16: AC Waveform: Program and Erase Operations (updated notes)

IPPR maximum specification change from ±25 µA to ±50 µA

Program and Erase Suspend Latency specification change

Updated Appendix A: Ordering Information (included 8 M and 4 M information)

Updated Figure, Appendix D: Architecture Block Diagram (Block info. in words not

bytes)

Minor wording changes

Combined byte-wide specification (previously 290605) with this document

Improved speed specification to 80 ns (3.0 V) and 90 ns (2.7 V)

Improved 1.8 V I/O option to minimum 1.65 V (Section 3.4)

Improved several DC characteristics (Section 4.4)

Improved several AC characteristics (Sections 4.5 and 4.6)

Combined 2.7 V and 1.8 V DC characteristics (Section 4.4)

Added 5 V VPP read specification (Section 3.4)

Removed 120 ns and 150 ns speed offerings

Moved Ordering Information from Appendix to Section 6.0; updated information

Moved Additional Information from Appendix to Section 7.0

Updated figure Appendix B, Access Time vs. Capacitive Load

Updated figure Appendix C, Architecture Block Diagram

Moved Program and Erase Flowcharts to Appendix E

Updated Program Flowchart

Updated Program Suspend/Resume Flowchart

Minor text edits throughout.

Added 32-Mbit density

Added 98H as a reserved command (Table 4)

A1–A20 = 0 when in read identifier mode (Section 3.2.2)

Status register clarification for SR3 (Table 7)

VCC and VCCQ absolute maximum specification = 3.7 V (Section 4.1)

Combined IPPW and ICCW into one specification (Section 4.4)

Combined IPPE and ICCE into one specification (Section 4.4)

Max Parameter Block Erase Time (tWHQV2/tEHQV2) reduced to 4 sec (Section 4.7)

Max Main Block Erase Time (tWHQV3/tEHQV3) reduced to 5 sec (Section 4.7)

Erase suspend time @ 12 V (tWHRH2/tEHRH2) changed to 5 µs typical and 20 µs

maximum (Section 4.7)

Ordering Information updated (Section 6.0)

Write State Machine Current/Next States Table updated (Appendix A)

Program Suspend/Resume Flowchart updated (Appendix F)

Erase Suspend/Resume Flowchart updated (Appendix F)

Text clarifications throughout

µBGA package diagrams corrected (Figures 3 and 4)

IPPD test conditions corrected (Section 4.4)

32-Mbit ordering information corrected (Section 6)

µBGA package top side mark information added (Section 6)

4

PRELIMINARY