STV7697A Ver la hoja de datos (PDF) - STMicroelectronics

Número de pieza

componentes Descripción

Fabricante

STV7697A Datasheet PDF : 16 Pages

| |||

STV7697A

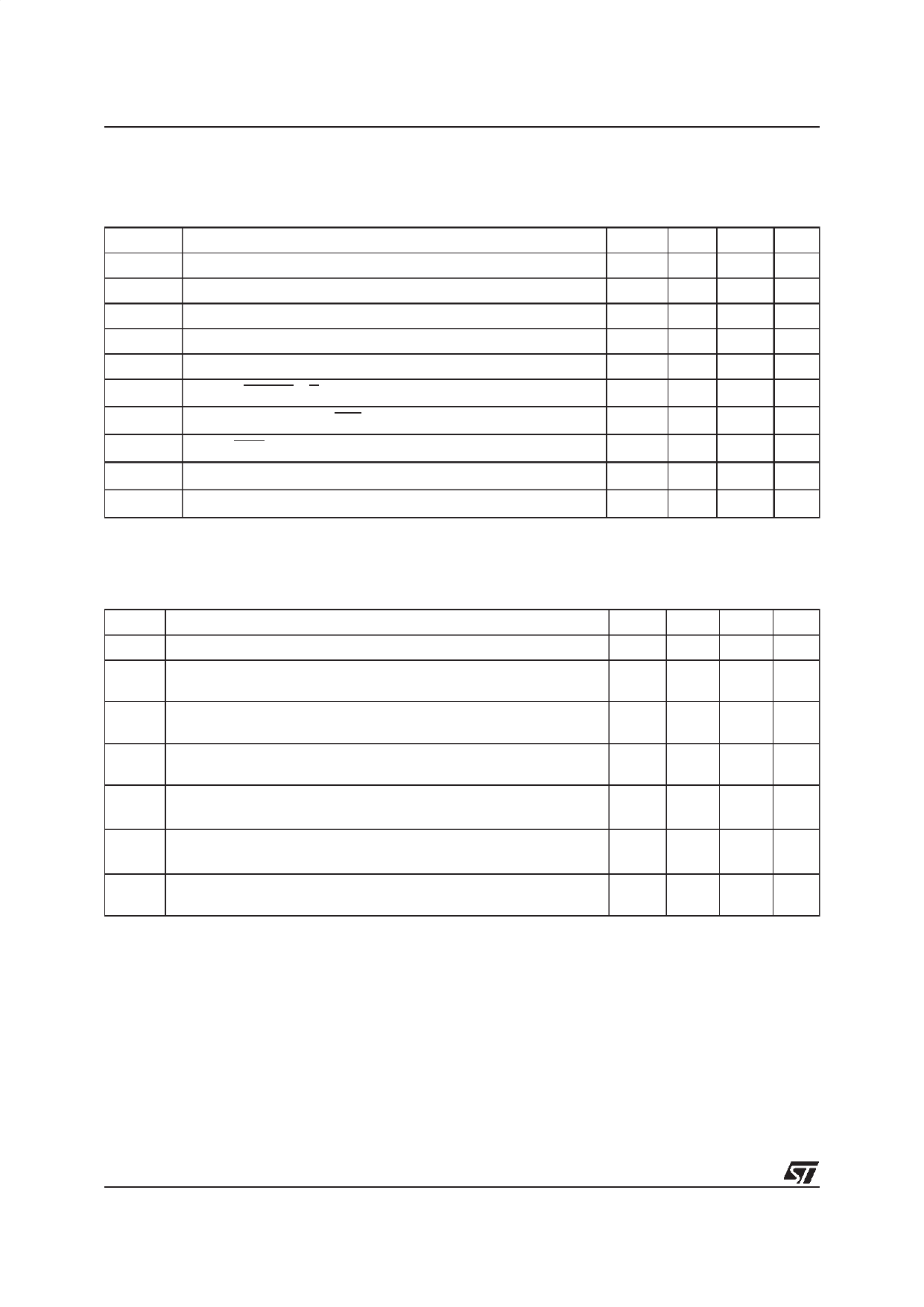

AC TIMINGS REQUIREMENTS

(VCC = 4.5 V to 5.5 V, Tamb = -20 to +85°C, input signals max leading edge & trailing edge (tR, tF) = 10 ns)

Symbol

Parameter

Min. Typ. Max. Unit

tCLK

tWHCLK

tWHCLK

tSDAT

tHDAT

tSFR

tDSTB

tSTB

tBLK

tPOL

Data Clock Period

Duration of clock (CLK) pulse at high level

Duration of clock (CLK) pulse at low level

Set-up Time of data input before clock low to high transition

Hold Time of data input after clock low to high transition

Forward/reverse (F/R) Set-up Time before low to high transition

Minimum Delay to latch STB after clock low to high transition

Strobe STB Pulse Duration

Blank (BLK) Pulse Duration

Polarity (POL) Pulse Duration

50

-

15

-

15

-

10

-

10

-

100

-

10

-

20

-

500

-

500

-

-

ns

-

ns

-

ns

-

ns

-

ns

-

ns

-

ns

-

ns

-

ns

-

ns

AC TIMINGS CHARACTERISTICS

(VCC = 5 V, VPP = 90 V, VSSP = 0 V, VSSLOG = VSSSUB = 0 V, Tamb = 25°C, fCLK = 20 MHz, VILMax. = 0.2

Vcc, VIHMin. = 0.8 VCC, VOH = 4.0 V, VOL = 0.4 V, CL = 15pF, unless otherwise specified)

Symbol

Parameter

tCLK

tRDAT

tFDAT

tPHL1

tPLH1

tPHL2

tPLH2

tPHL3

tPLH3

Data Clock Period

Logical Data Output Rise Time

Logical Data Output Fall Time

Delay of logic data output after clock (CLK) high to low transition

Delay of logic data output after clock (CLK) low to high transition

Delay of power output change after clock (CLK) high to low transition

Delay of power output change after clock (CLK) low to high transition

Delay of power output change after blanking (BLK) high to low transition

Delay of power output change after blanking (BLK) low to high transition

tPHL4 Delay of power output change after polarity (POL) high to low transition

tPLH4 Delay of power output change after polarity (POL) low to high transition

tROUT Power Output Rise Time (7)

tFOUT Power Output Fall Time (7)

Min.

50

-

-

-

-

-

-

-

-

-

-

-

-

Typ. Max. Unit

-

-

ns

20

-

ns

11

-

ns

45

80

ns

48

80

ns

120 180 ns

120 180 ns

110 165 ns

110 165 ns

-

160 ns

-

160 ns

100 200 ns

60

200 ns

Note 7 One output among 64, loading capacitor COUT = 100pF, other outputs at low level.

10/15

3