SA9101 Ver la hoja de datos (PDF) - South African Micro Electronic Systems

Número de pieza

componentes Descripción

Fabricante

SA9101 Datasheet PDF : 40 Pages

| |||

SA9101

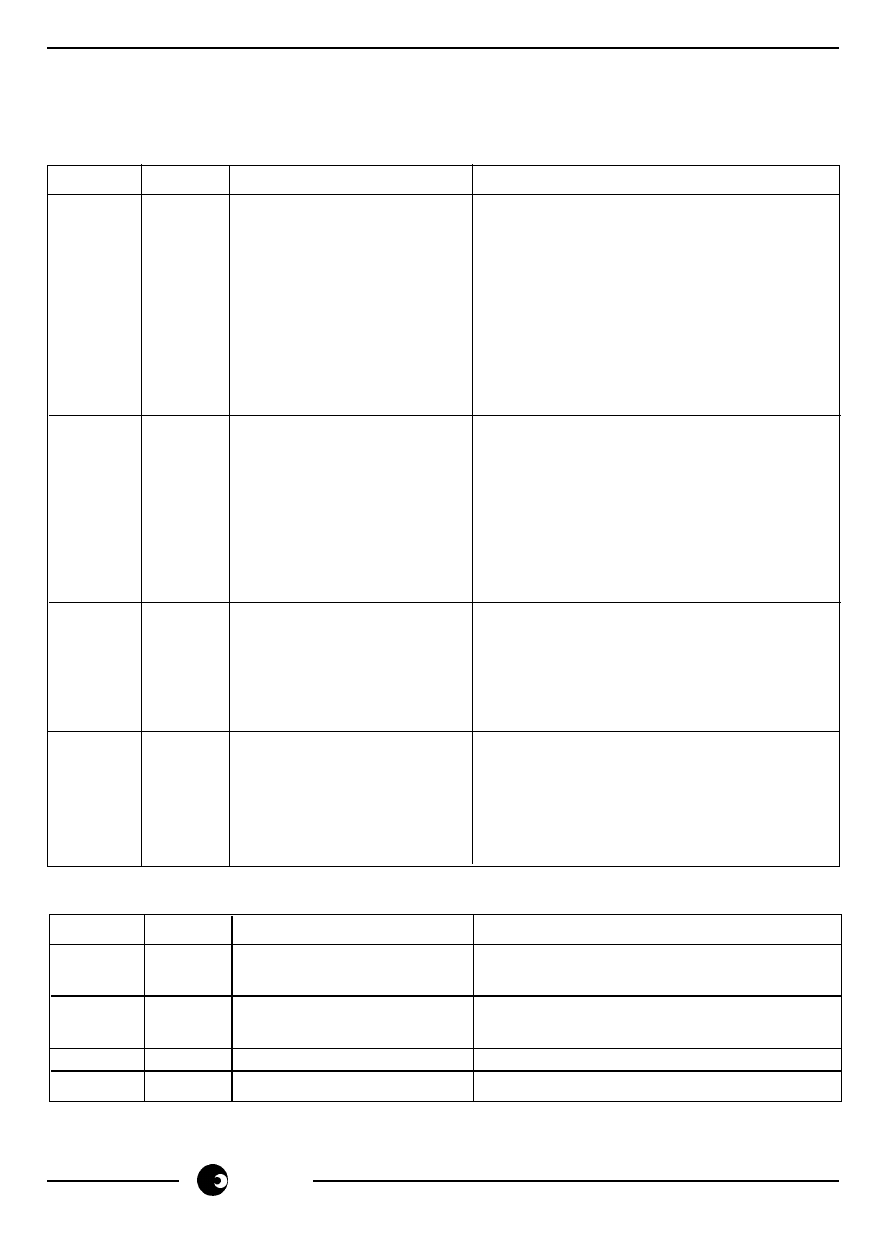

DESCRIPTION OF INTERFACES

Fibre Optical Interface

The fibre optical interface is enabled via the microprocessor interface.

Signal

Pin Input/Output/Bidirect Function

OPIN

29

I

Optical Fibre In

Unipolar Input Signal at 2048 kbps

Input polarity sense is programmable

via CR8B3. Latching of data is

performed with the falling edge of

RCLK if optical interface is selected

via CR1B2. (See Fig. 6 Line Interface

Timing.)

OPOUT

6

O

Optical Fibre Out

Unipolar Output Signal at 2048 kbps

The output's active polarity is

programmable via CR6B7. Data is

clocked out on the rising edge of

XRCLK. Data duty cycle is 100%.

(See Fig. 6 Line Interface Timing.)

RCLK

25

I

Route Clock

This clock, derived from the incoming

data by the line interface circuit (eg.

IPAT (PEB2235)), is necessary for

clocking received data into the SA9101.

XRCLK

37

O

Transmit Route Clock

This 2048kHz clock is generated from

the Station Clock, SCLK. (See Fig. 5

System Interface Timing and Fig. 6

Line Interface Timing.)

PCM30 Interface

Signal Pin

DRA

27,

DRB

26

DXA

38,

DXB

39

RCLK

25

XRCLK 37

Input/Output/Bidirect

I

I

O

O

I

O

Function

Data Receive +/-

HDB3 coded PCM Signal

Data transmit +/-

HDB3 coded PCM Signal

Route Clock f = 2.048 MHz

Transmit route clock

6/40

sames