SA9101 Ver la hoja de datos (PDF) - South African Micro Electronic Systems

Número de pieza

componentes Descripción

Fabricante

SA9101 Datasheet PDF : 40 Pages

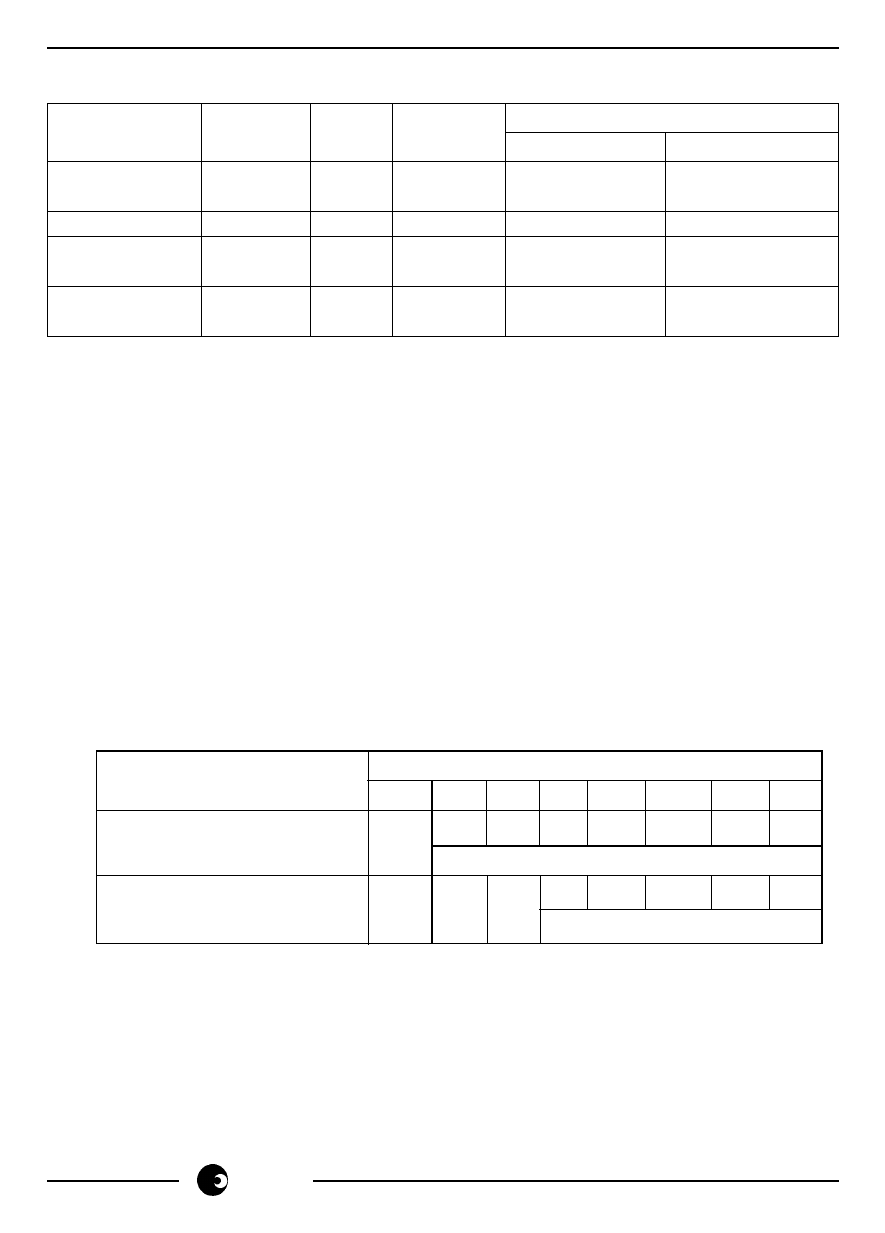

| |||

SA9101

Transparent Framing A Bit

Mode

(incl. CRC)

Non-Transparent Internally

generated

CR5B5

via DXI

CR5B4

Internally

generated

CX1B6

Internally

generated

CR4B5

via DXI

CR4B5

CR4B5

Sn bits

CR4B0..41

Si bits

Double frame

CRC

CR4B7 & CR5B2 CR5B0 & CR5B12

via DXI

via DXI

via DXI

via DXI

via DXI

via DXI

via DXI CR4B7 & CR5B2 CR5B0 & CR5B12

Notes: 1) The Sn bit stack may be used optionally

2) Automatic transmission of submultiframe error indication is selectable

General signalling

- S (Y) bits.

n

- Si bits.

Signalling

- CCS: For Common Channel Signalling the use of timeslot 16 is recommended. The

use of CCS is allowed with both the doubleframe and the CRC-Multiframe format.

- CAS-CC: For Channel Associated Signalling the use of timeslot 16 is recommended.

The autonomous CAS multiframe structure is not related to a doubleframe or a CRC-

Multiframe structure (refer to CCITT G704 paragraph 3.3.3). Note: CAS multiframe

synchronization and syntheses are not performed by the SA9101.

Doubleframe format

The framing structure is defined by the contents of timeslot 0 (refer to table 1).

Alternate Frames

Bit Number

1

23 4 5 6 7 8

Frame containing the frame Si

00 1 1 0 1 1

alignment signal

Note 1

Frame alignment signal

Frame not containing the

frame alignment signal

S 1 AS S S S S

i

n0

n1

n2

n3

n4

Note 1 Note 2 Note 3

Note 4

Table 1: Allocation of bits 1 to 8 of Timeslot 0

14/40

sames