74F373 Ver la hoja de datos (PDF) - Philips Electronics

Número de pieza

componentes Descripción

Fabricante

74F373

74F373 Datasheet PDF : 12 Pages

| |||

Philips Semiconductors

Latch/flip-flop

Product specification

74F373/74F374

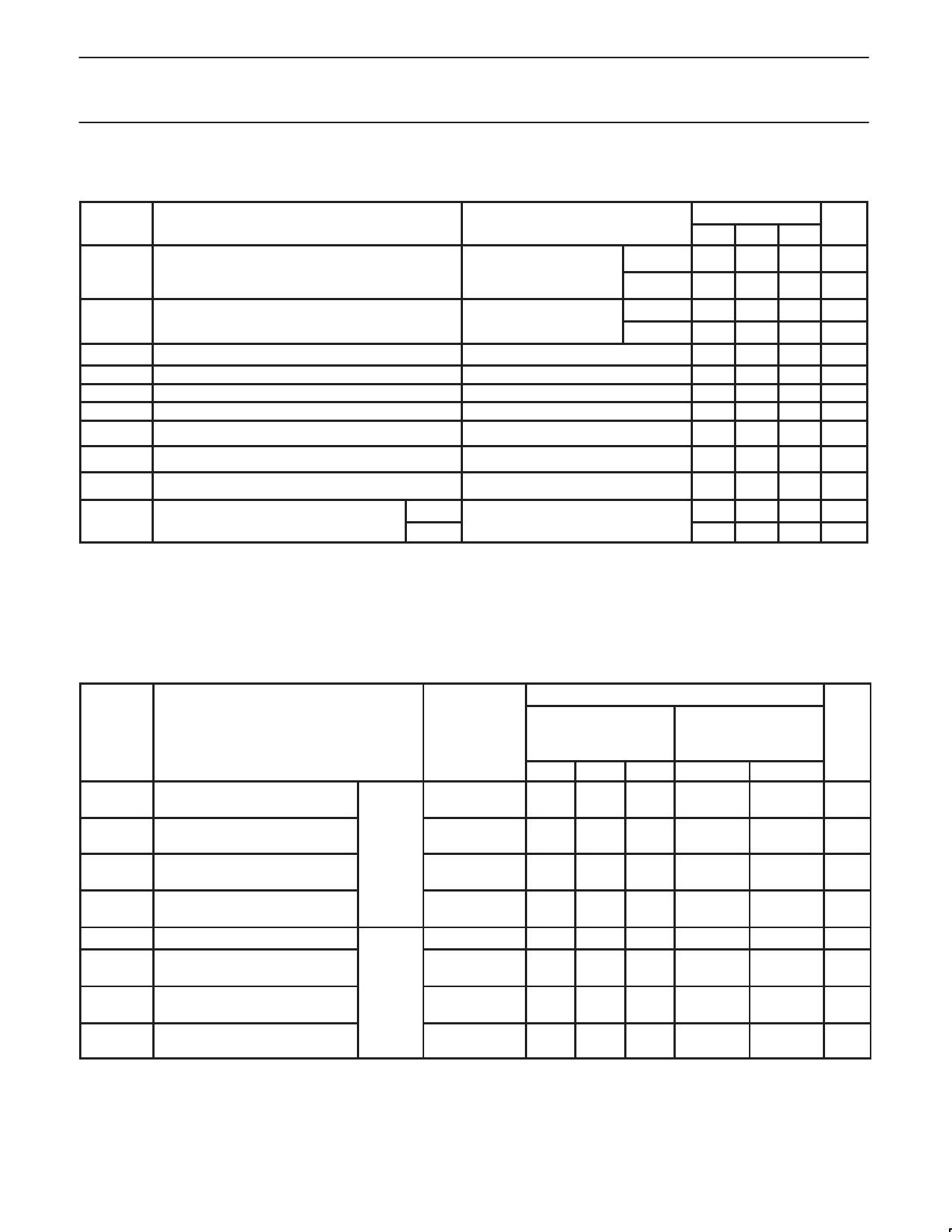

DC ELECTRICAL CHARACTERISTICS

(Over recommended operating free-air temperature range unless otherwise noted.)

SYMBOL

PARAMETER

TEST

CONDITIONS1

LIMITS

UNIT

MIN TYP2 MAX

VOH

High-level output voltage

VCC = MIN, VIL = MAX,

±10%VCC 2.4

V

VIH = MIN, IOH = MAX

±5%VCC 2.7 3.4

V

VOL

VIK

II

IIH

IIL

IOZH

Low-level output voltage

Input clamp voltage

Input current at maximum input voltage

High-level input current

Low-level input current

Off-state output current, high-level voltage applied

VCC = MIN, VIL = MAX,

VIH = MIN, IOL = MAX

VCC = MIN, II = IIK

VCC = MAX, VI = 7.0V

VCC = MAX, VI = 2.7V

VCC = MAX, VI = 0.5V

VCC = MAX, VO = 2.7V

±10%VCC

±5%VCC

0.35 0.50 V

0.35 0.50 V

-0.73 -1.2 V

100 µA

20 µA

-0.6 mA

50 µA

IOZL

Off-state output current, low-level voltage applied

VCC = MAX, VO = 0.5V

IOS

Short-circuit output current3

VCC = MAX

-50 µA

-60

-150 mA

ICC

Supply current (total)

74F373

VCC = MAX

74F374

35 60 mA

57 86 mA

NOTES:

1. For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions for the applicable type.

2. All typical values are at VCC = 5V, Tamb = 25°C.

3. Not more than one output should be shorted at a time. For testing IOS, the use of high-speed test apparatus and/or sample-and-hold

techniques are preferable in order to minimize internal heating and more accurately reflect operational values. Otherwise, prolonged shorting

of a high output may raise the chip temperature well above normal and thereby cause invalid readings in other parameter tests. In any

sequence of parameter tests, IOS tests should be performed last.

AC ELECTRICAL CHARACTERISTICS

SYMBOL

PARAMETER

tPLH

tPHL

tPLH

tPHL

tPZH

tPZL

tPHZ

tPLZ

fmax

tPLH

tPHL

tPZH

tPZL

tPHZ

tPLZ

Propagation delay

Dn to Qn

Propagation delay

E to Qn

Output enable time

to high or low level

Output disable time

from high or low level

Maximum clock frequency

Propagation delay

CP to Qn

Output enable time

to high or low level

Output disable time

from high or low level

74F373

74F374

TEST

CONDITION

Waveform 3

Waveform 2

Waveform 6

Waveform 7

Waveform 6

Waveform 7

Waveform 1

Waveform 1

Waveform 6

Waveform 7

Waveform 6

Waveform 7

LIMITS

Tamb = +25°C

VCC = +5.0V

CL = 50pF, RL = 500Ω

Tamb = 0°C to +70°C

VCC = +5.0V ± 10%

CL = 50pF, RL = 500Ω

MIN TYP MAX

MIN

MAX

3.0

5.3

7.0

3.0

8.0

2.0

3.7

5.0

2.0

6.0

5.0 9.0 11.5

5.0

12.0

3.0

4.0

7.0

3.0

8.0

2.0 5.0 11.0

2.0

11.5

2.0

5.6

7.5

2.0

8.5

2.0

4.5

6.5

2.0

7.0

2.0

3.8

5.0

2.0

6.0

150 165

140

3.5

5.0

7.5

3.0

8.5

3.5

5.0

7.5

3.0

8.5

2.0 9.0 11.0

2.0

12.0

2.0

5.3

7.5

2.0

8.5

2.0

5.3

6.0

2.0

7.0

2.0

4.3

5.5

2.0

6.5

UNIT

ns

ns

ns

ns

ns

ns

ns

ns

December 5, 1994

6