SA9110AFA Ver la hoja de datos (PDF) - South African Micro Electronic Systems

Número de pieza

componentes Descripción

Fabricante

SA9110AFA

SA9110AFA Datasheet PDF : 18 Pages

| |||

SA9110A

Memory Reset

In programming mode (while PGM is pulled low) if PCLK is left floating and PDTA=0,

the internal clock of the SA9110A will ensure that default values are set. For default

conditions all of the RAM locations are set to 0 and the value of the slope is set to

11389.

The minimum time period for a complete reset cycle is determined by:

tmin

= 322 * 64

FOSC

Where FOSC = Oscillator frequency (2MHz.....4MHz)

If the recommended crystal frequency of 3.5795MHz is used, this will result in a

minimum reset time of 5.8ms.

The specified signal levels on pins PGM, PCLK and PDTA must remain stable for

the entire reset cycle period.

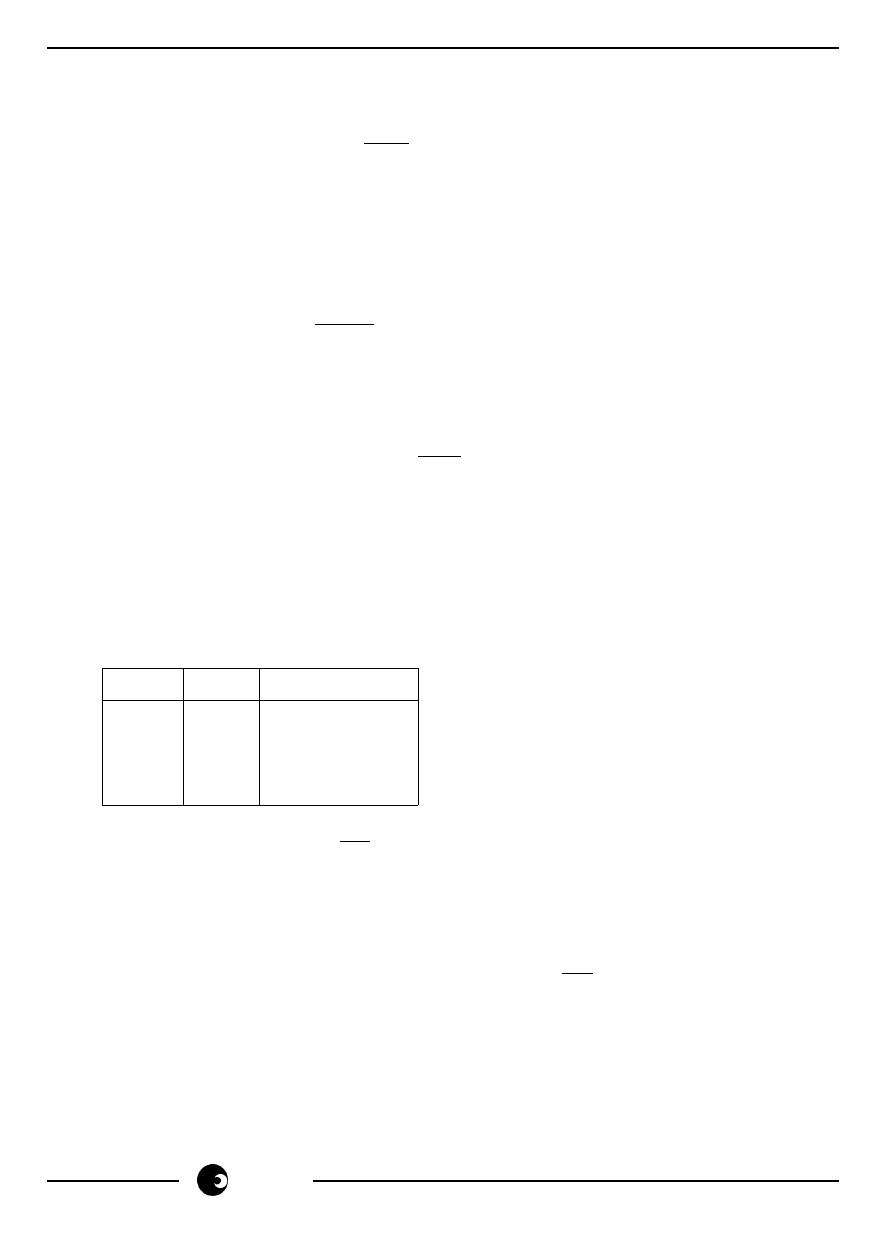

5. Tariff Registers

A multiple tariff facility is provided on-chip by means of 4 tariff registers, which are

externally selectable via the SR[0] and SR[1] inputs. The registers may be selected

by programming the SR[0] and SR[1] inputs as follows:

SR[1]

0

0

1

1

SR[0]

0

1

0

1

Register

Register 1

Register 2

Register 3

Register 4

The 4 tariff registers as well as the total register may be sequentially displayed by

activating the Push Button (PB). The minimum Push Button make time is 5mS. The

contents of the register selected for display is retained on the display for a period

of 10 seconds, provided that the push button is not activated during this period. After

the 10 seconds has elapsed, the display defaults to the "active" register defined by

the status of the SR[0] and SR[1] inputs.

The register selected for display via the push button (PB) is indicated by the relevant

announciator.

12/18

sames