BR24T16FJ-WZE2 Ver la hoja de datos (PDF) - ROHM Semiconductor

Número de pieza

componentes Descripción

Fabricante

BR24T16FJ-WZE2 Datasheet PDF : 41 Pages

| |||

BR24T16-W

Datasheet

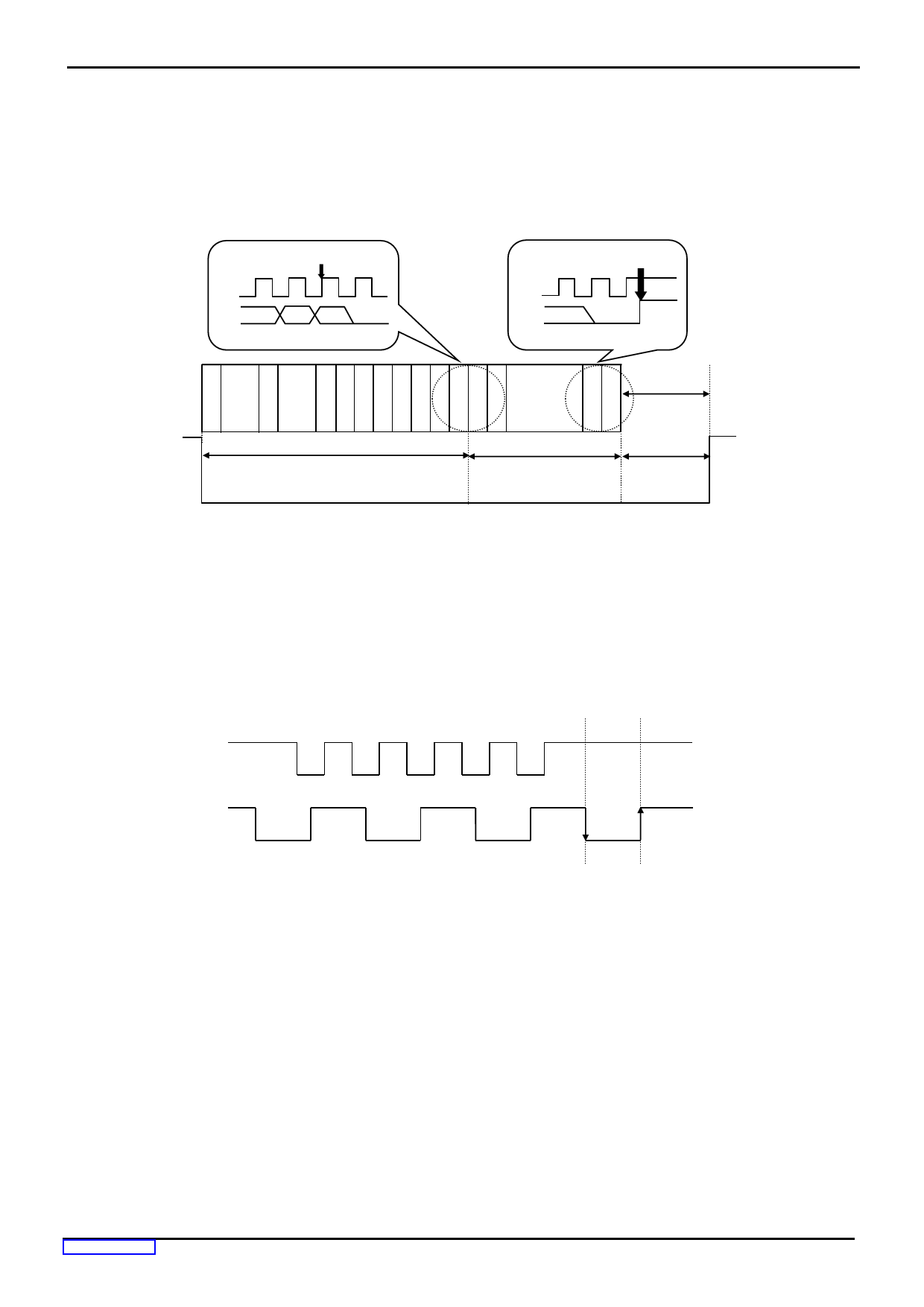

WP Valid Timing (Write Cancel)

WP is usually fixed to 'H' or 'L', but when WP is used to cancel write cycle and so on, pay attention to the following WP valid

timing. During write cycle execution, inside cancel valid area, by setting WP='H', write cycle can be cancelled. In both byte

write cycle and page write cycle, the area from the first start condition of command to the rise of clock to take in D0 of data(in

page write cycle, the first byte data) is the cancel invalid area.

WP input in this area becomes ‘Don't care’. The area from the rise of SCL to take in D0 to the stop condition input is the

cancel valid area. Furthermore, after the execution of forced end by WP, the IC enters standby status.

·Rise of D0 taken clock

SCL

SDA

D1 D0 ACK

Enlarged view

·Rise of SDA

SCL

SDA D0 ACK

Enlarged view

SDA

WP

S

T Slave

A

R Address

T

A

C Word

K

L

Address

A

C

K

L

A

D7 D6 D5 D4 D3 D2 D1 D0 C

K

L

Data

AS

CT

KO

LP

tWR

WP cancel invalid area

WP cancel valid area WP cancel invalid area

Data is not written.

Figure 42. WP Valid Timing

Command Cancel by Start Condition and Stop Condition

During command input, by continuously inputting start condition and stop condition, command can be cancelled. (Figure 43.)

However, within ACK output area and during data read, SDA bus may output 'L'. In this case, start condition and stop condition

cannot be input, so reset is not available. Therefore, execute software reset. When command is cancelled by start-stop

condition during random read cycle, sequential read cycle, or current read cycle, internal setting address is not determined.

Therefore, it is not possible to carry out current read cycle in succession. To carry out read cycle in succession, carry out

random read cycle.

SCL

SDA

1

0

1

0

Start condition Stop condition

Figure 43. Case of Cancel by Start, Stop Condition during Slave Address Input

www.rohm.com

©2012 ROHM Co., Ltd. All rights reserved.

TSZ22111 • 15 • 001

17/36

TSZ02201-0R2R0G100110-1-2

24.Dec.2020 Rev.008