ATSAMA5D42A-CU Ver la hoja de datos (PDF) - Atmel Corporation

Número de pieza

componentes Descripción

Fabricante

ATSAMA5D42A-CU Datasheet PDF : 1808 Pages

| |||

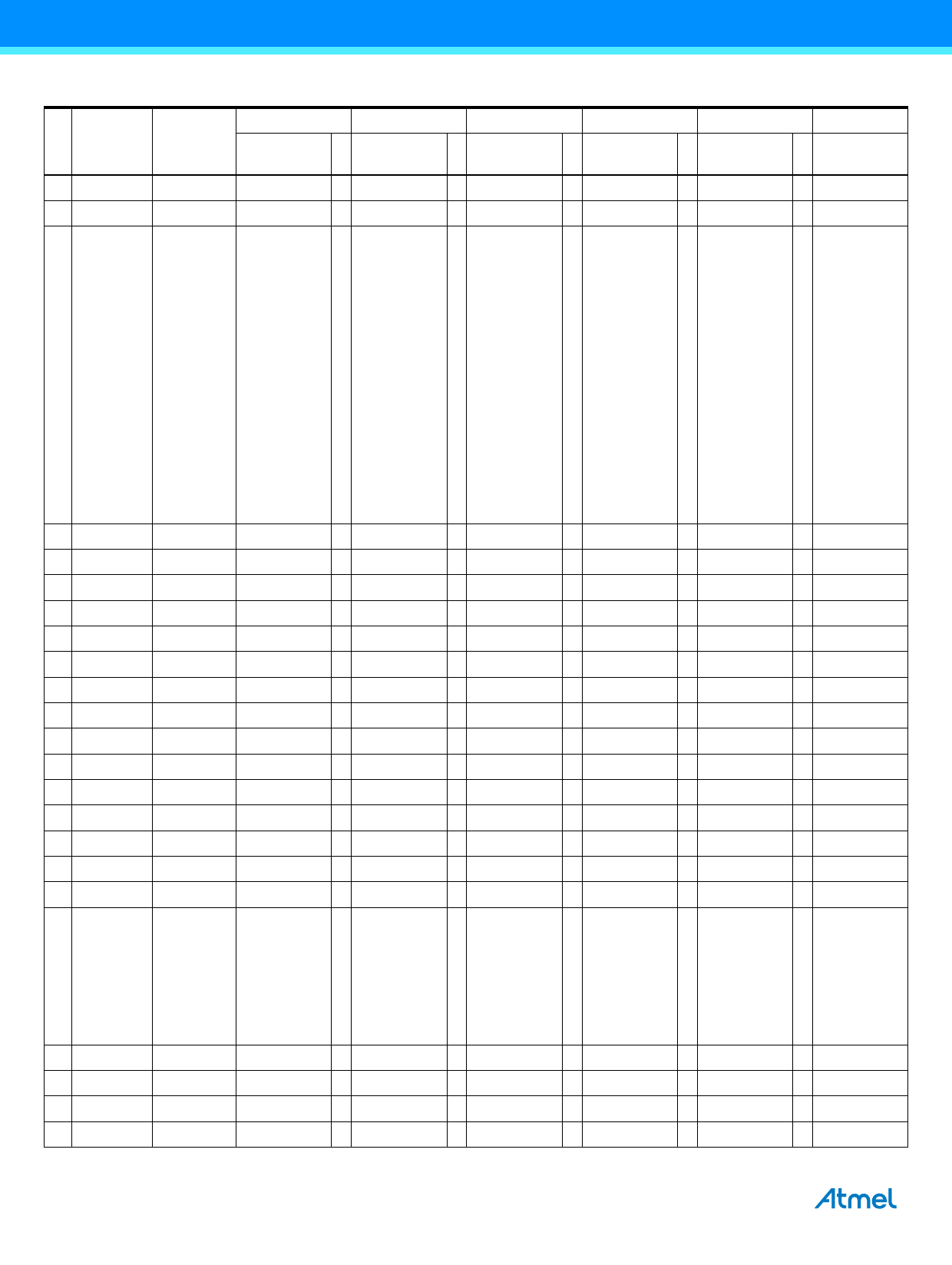

Table 3-1. TFBGA361 Pin Description (Continued)

Primary

Alternate

PIO Peripheral A PIO Peripheral B PIO Peripheral C Reset State

Pin Power Rail I/O Type

Signal, Dir, PU,

Signal Dir Signal Dir Signal Dir Signal Dir Signal Dir PD, HiZ, ST

U2 VDDIOP

DIB

PE30

I/O

–

–

DIBN

O UTXD0 O TWCK1 O PIO, O, LOW

L4 VDDIOP

GPIO

PE31

I/O

–

–

ADTRG

I

–

–

–

– PIO, O, LOW

H10

G10

K10

J10

K9

J9

H9

G9

E7

A8

–

Not connected

–

–

–

–

–

–

–

–

–

–

–

D7

B7

C7

E9

A10

B9

D8

A9

P4 VDDBU

SYSC

TST

I

–

–

–

–

–

–

–

– I, PD, ST

W12 VDDIOP

CLOCK

XIN

I

–

–

–

–

–

–

–

–

I

V12 VDDIOP

CLOCK

XOUT

O

–

–

–

–

–

–

–

–

O

W2 VDDBU

CLOCK

XIN32

I

–

–

–

–

–

–

–

–

I

W3 VDDBU

CLOCK

XOUT32 O

–

–

–

–

–

–

–

–

O

T2 VDDBU

SYSC

SHDN

O

–

–

–

–

–

–

–

–

O, PU

V3 VDDBU

SYSC

WKUP

I

–

–

–

–

–

–

–

–

I, ST

U3 VDDBU

PIOBU

PIOBU0 I

–

–

–

–

–

–

–

–

I, PU

T3 VDDBU

PIOBU

PIOBU1 I

–

–

–

–

–

–

–

–

I, PU

T4 VDDBU

PIOBU

PIOBU2 I

–

–

–

–

–

–

–

–

I, PU

U4 VDDBU

PIOBU

PIOBU3 I

–

–

–

–

–

–

–

–

I, PU

P6 VDDBU

PIOBU

PIOBU4 I

–

–

–

–

–

–

–

–

I, PU

T5 VDDBU

PIOBU

PIOBU5 I

–

–

–

–

–

–

–

–

I, PU

R4 VDDBU

PIOBU

PIOBU6 I

–

–

–

–

–

–

–

–

I, PU

U5 VDDBU

PIOBU

PIOBU7 I

–

–

–

–

–

–

–

–

I, PU

R5

U6

R6

T6

R7

–

Not connected

–

–

–

–

–

–

–

–

–

–

–

U7

P7

T7

T1 VDDBU

RST

NRST

I

–

–

–

–

–

–

–

–

I

V2 VDDBU

SYSC

JTAGSEL I

–

–

–

–

–

–

–

–

I, PD

F15 VDDIODDR DDR_IO

DDR_A0 O

–

–

–

–

–

–

–

– O, LOW

F16 VDDIODDR DDR_IO

DDR_A1 O

–

–

–

–

–

–

–

– O, LOW

14 SAMA5D4 Series [DATASHEET]

Atmel-11238C-ATARM-SAMA5D4-Datasheet_12-Jul-16