WM8721(2000) Ver la hoja de datos (PDF) - Wolfson Microelectronics plc

Número de pieza

componentes Descripción

Fabricante

WM8721 Datasheet PDF : 34 Pages

| |||

WM8721

Product Preview

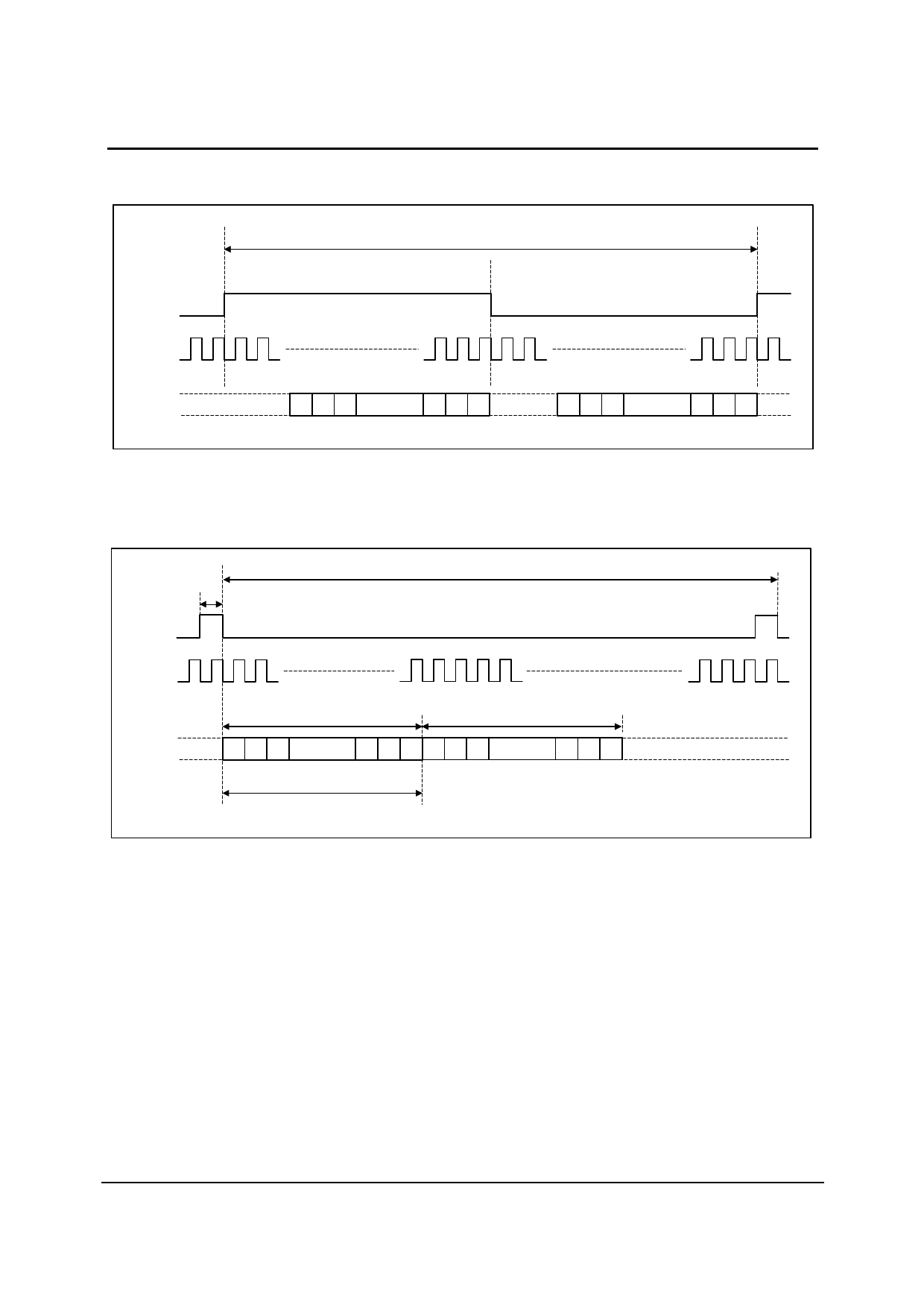

In Master mode, DACLRC will be output with a 50:50 mark-space ratio with BCLK output at 64fs. The

exception again is in USB mode where BCLK is always 12MHz. So for example in 12MHz/32k fs

mode there are 375 master clocks per LRC period. Therefore the DACLRC output will have a mark

space ratio of 187:188.

The DAC digital audio interface modes are software configurable as indicated in Table 7. Note that

dynamically changing the software format may result in erroneous operation of the interfaces and is

therefore not recommended.

The length of the digital audio data is programmable at 16/20/24 or 32 bits. Refer to the software

control table below. The data is signed 2’s complement. The DAC digital filters process data using 24

bits. If the DAC is programmed to receive 16 or 20 bit data, the WM8721 packs the LSBs with zeros.

If the DAC is programmed to receive 32 bit data, then it strips the LSBs.

The DAC outputs can be swapped under software control using LRP and LRSWAP as shown in

Table 7. Stereo samples are normally generated as a Left/Right sampled pair. LRSWAP reverses

the order of that a Left sample goes to the right DAC output and a Right sample goes to the left DAC

output. LRP swaps the phasing so that a Right/Left sampled pair is expected and preserves the

correct channel phase difference, except in DSP mode, where LRP controls the positioning of the

MSB relative to the rising edge of DACLRC.

DACDAT is always an input. It is expected to be set low by the audio interface controller when the

WM8721 is powered off or in standby.

DACLRC and BCLK can be either outputs or inputs depending on whether the device is configured

as a master or slave. If the device is a master then the DACLRC and BCLK signals are outputs that

default low. If the device is a slave then the DACLRC and BCLK are inputs. It is expected that these

are set low by the audio interface controller when the WM8721 is powered off or in standby.

WOLFSON MICROELECTRONICS LTD

PP Rev 1.3 November 2000

18