TSL2580 Ver la hoja de datos (PDF) - TEXAS ADVANCED OPTOELECTRONIC SOLUTIONS

Número de pieza

componentes Descripción

Fabricante

TSL2580 Datasheet PDF : 34 Pages

| |||

TSL2580, TSL2581

LIGHT-TO-DIGITAL CONVERTER

TAOS098 − MARCH 2010

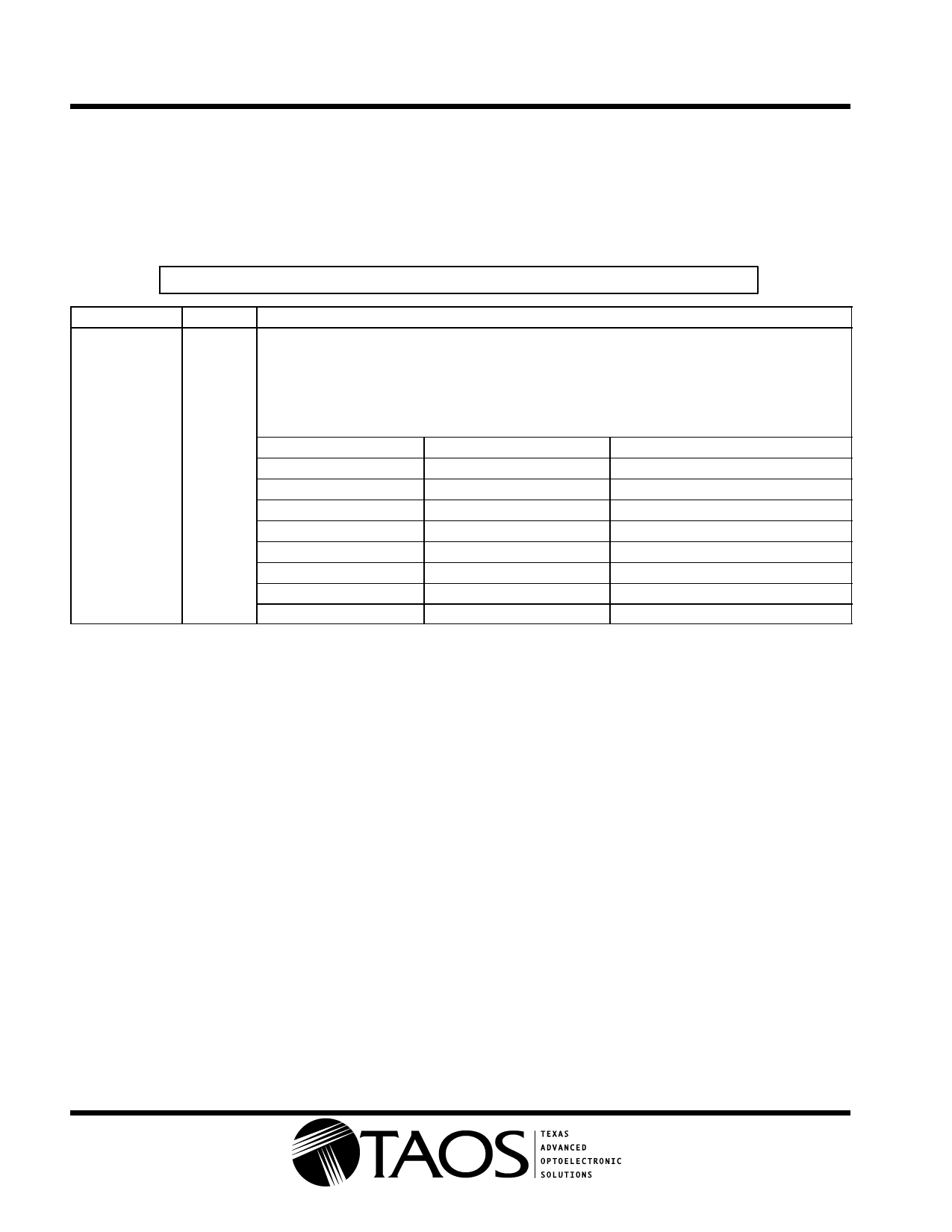

Timing Register (01h)

The TIMING register controls the internal integration time of the ADC channels in 2.7 ms increments. The

TIMING register defaults to 00h at power on.

Table 5. Timing Register

Bit : 7

Address

01h

FIELD

BIT

ITIME

7:0

6

5

4

3

2

1

0

ITIME

Reset

00h

DESCRIPTION

Integration Cycles. Specifies the integration time in 2.7-ms intervals. Time is expressed as a 2’s

complement number. So, to quickly work out the correct value to write: (1) determine the number of

2.7-ms intervals required, and (2) then take the 2’s complement. For example, for a 1 × 2.7-ms interval,

0xFF should be written. For 2 × 2.7-ms intervals, 0xFE should be written. The maximum integration time

is 688.5 ms (00000001b).

Writing a 0x00 to this register is a special case and indicates manual timing mode. See CONTROL and

MANUAL INTEGRATION TIMER Registers for other device options related to manual integration.

INTEG_CYCLES

TIME

VALUE

−

Manual integration

00000000

1

2.7 ms

11111111

2

5.4 ms

11111110

19

51.3 ms

11101101

37

99.9 ms

11011011

74

199.8 ms

10110110

148

399.6 ms

01101100

255

688.5 ms

00000001

NOTE: The Send Byte protocol cannot be used when ITIME is greater than 127 (for example ITIME[7] = 1) since the upper bit is set aside for

write transactions in the COMMAND register.

Interrupt Register (02h)

The INTERRUPT register controls the extensive interrupt capabilities of the device. The open-drain interrupt

pin is active low and requires a pull-up resistor to VDD in order to pull high in the inactive state. The TSL258x

permits both SMB-Alert style interrupts as well as traditional level style interrupts. The Interrupt Register

provides control over when a meaningful interrupt will occur. The concept of a meaningful change can be defined

by the user both in terms of light intensity and time, or persistence of that change in intensity. The value must

cross the threshold (as configured in the Threshold Registers 03h through 06h) and persist for some period of

time as outlined in Table 6.

When a level Interrupt is selected, an interrupt is generated whenever the last conversion results in a value

outside of the programmed threshold window. The interrupt is active-low and remains asserted until cleared by

writing an 11 in the TRANSACTION field in the COMMAND register.

In SMB-Alert mode, the interrupt is similar to the traditional level style and the interrupt line is asserted low. To

clear the interrupt, the host responds to the SMB-Alert by performing a modified Receive Byte operation, in

which the Alert Response Address (ARA) is placed in the slave address field, and the TSL258x that generated

the interrupt responds by returning its own address in the seven most significant bits of the receive data byte.

If more than one device connected on the bus has pulled the SMBAlert line low, the highest priority (lowest

address) device will win control of the bus during the slave address transfer. If the device loses this arbitration,

the interrupt will not be cleared. The Alert Response Address is 0Ch.

Copyright E 2010, TAOS Inc.

14

r

www.taosinc.com

The LUMENOLOGY r Company

r