W83194R-81 Ver la hoja de datos (PDF) - Winbond

Número de pieza

componentes Descripción

Fabricante

W83194R-81 Datasheet PDF : 18 Pages

| |||

W83194R-81

10.0 POWER MANAGEMENT TIMING

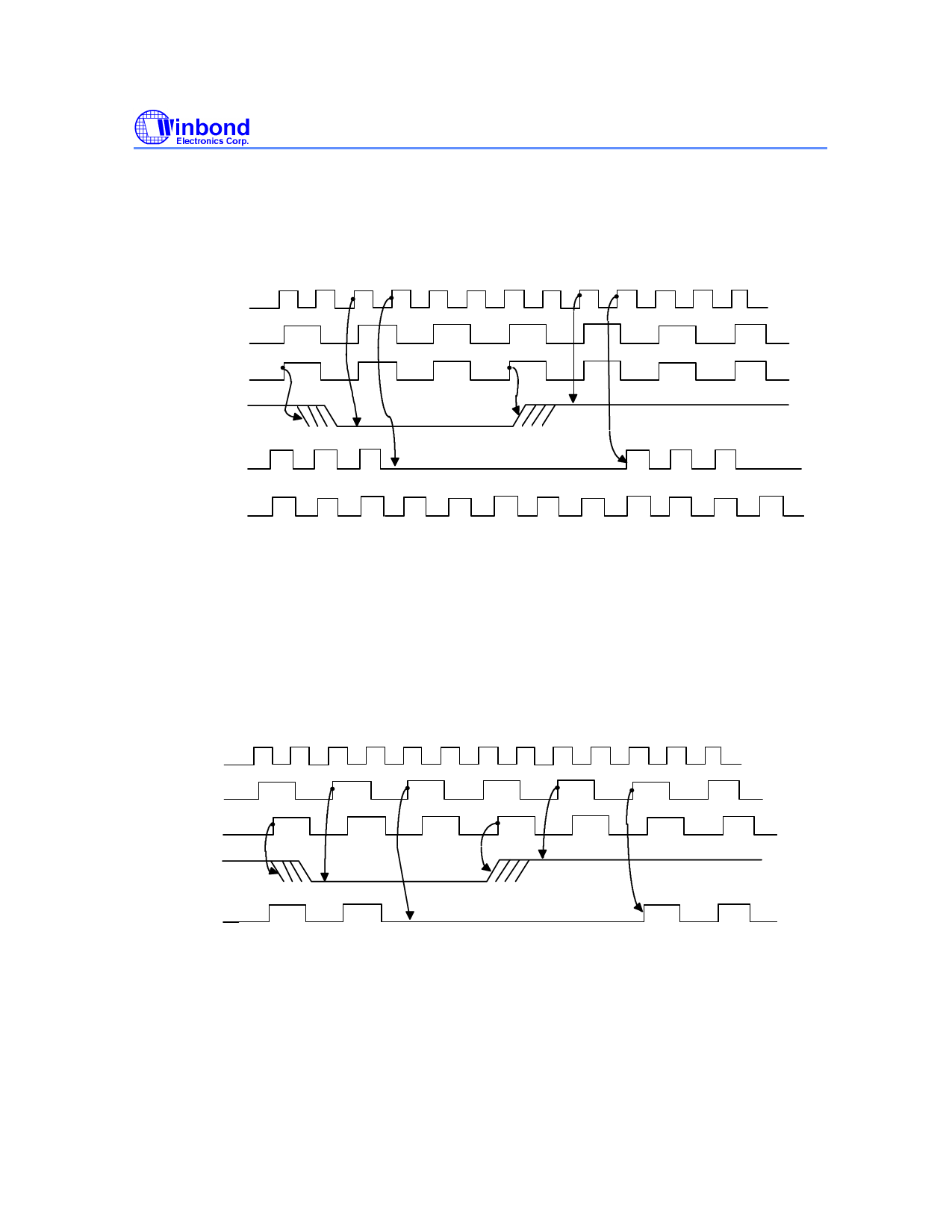

10.1 CPU_STOP# Timing Diagram

CPUCLK

(Internal)

1

2

PCICLK

(Internal)

PCICLK_F

CPU_STOP#

PRELIMINARY

1

2

CPUCLK[0:3]

SDRAM

For synchronous Chipset, CPU_STOP# pin is a synchronous “active low ”input pin used to stop the

CPU clocks for low power operation. This pin is asserted synchronously by the external control logic

at the rising edge of free running PCI clock(PCICLK_F). All other clocks will continue to run while

the CPU clocks are stopped. The CPU clocks will always be stopped in a low state and resume

output with full pulse width. In this case, CPU locks on latency“ is less than 2 CPU clocks and

locks off latency is less then 2 CPU clocks.

10.2 PCI_STOP# Timing Diagram

CPUCLK

(Internal)

PCICLK

(Internal)

PCICLK_F

PCI_STOP#

1

2

1

2

PCICLK[0:4]

For synchronous Chipset, PCI_STOP# pin is a synchronous ctive low” input pin used to stop the

PCICLK [0:4] for low power operation. This pin is asserted synchronously by the external control logic

at the rising edge of free running PCI clock(PCICLK_F). All other clocks will continue to run while

the PCI clocks are stopped. The PCI clocks will always be stopped in a low state and resume output

with full pulse width. In this case, PCI locks on latency“ is less than 1 PCI clocks and locks off

latency is less then 1 PCI clocks.

- 16 -

Publication Release Date: Dec. 1998

Revision 0.20