M95160-RMC6G(2014) Ver la hoja de datos (PDF) - STMicroelectronics

Número de pieza

componentes Descripción

Fabricante

M95160-RMC6G Datasheet PDF : 47 Pages

| |||

Operating features

M95160 M95160-W M95160-R M95160-DF

5.1.4

Power-down

During power-down (continuous decrease of the VCC supply voltage below the minimum

VCC operating voltage defined under Operating conditions in Section 9: DC and AC

parameters), the device must be:

• deselected (Chip Select S should be allowed to follow the voltage applied on VCC),

• in Standby Power mode (there should not be any internal write cycle in progress).

5.2

Active Power and Standby Power modes

When Chip Select (S) is low, the device is selected, and in the Active Power mode. The

device consumes ICC.

When Chip Select (S) is high, the device is deselected. If a Write cycle is not currently in

progress, the device then goes into the Standby Power mode, and the device consumption

drops to ICC1, as specified in DC characteristics (see Section 9: DC and AC parameters).

5.3

Hold condition

The Hold (HOLD) signal is used to pause any serial communications with the device without

resetting the clocking sequence.

To enter the Hold condition, the device must be selected, with Chip Select (S) low.

During the Hold condition, the Serial Data Output (Q) is high impedance, and the Serial Data

Input (D) and the Serial Clock (C) are Don’t Care.

Normally, the device is kept selected for the whole duration of the Hold condition.

Deselecting the device while it is in the Hold condition has the effect of resetting the state of

the device, and this mechanism can be used if required to reset any processes that had

been in progress.(a) (b)

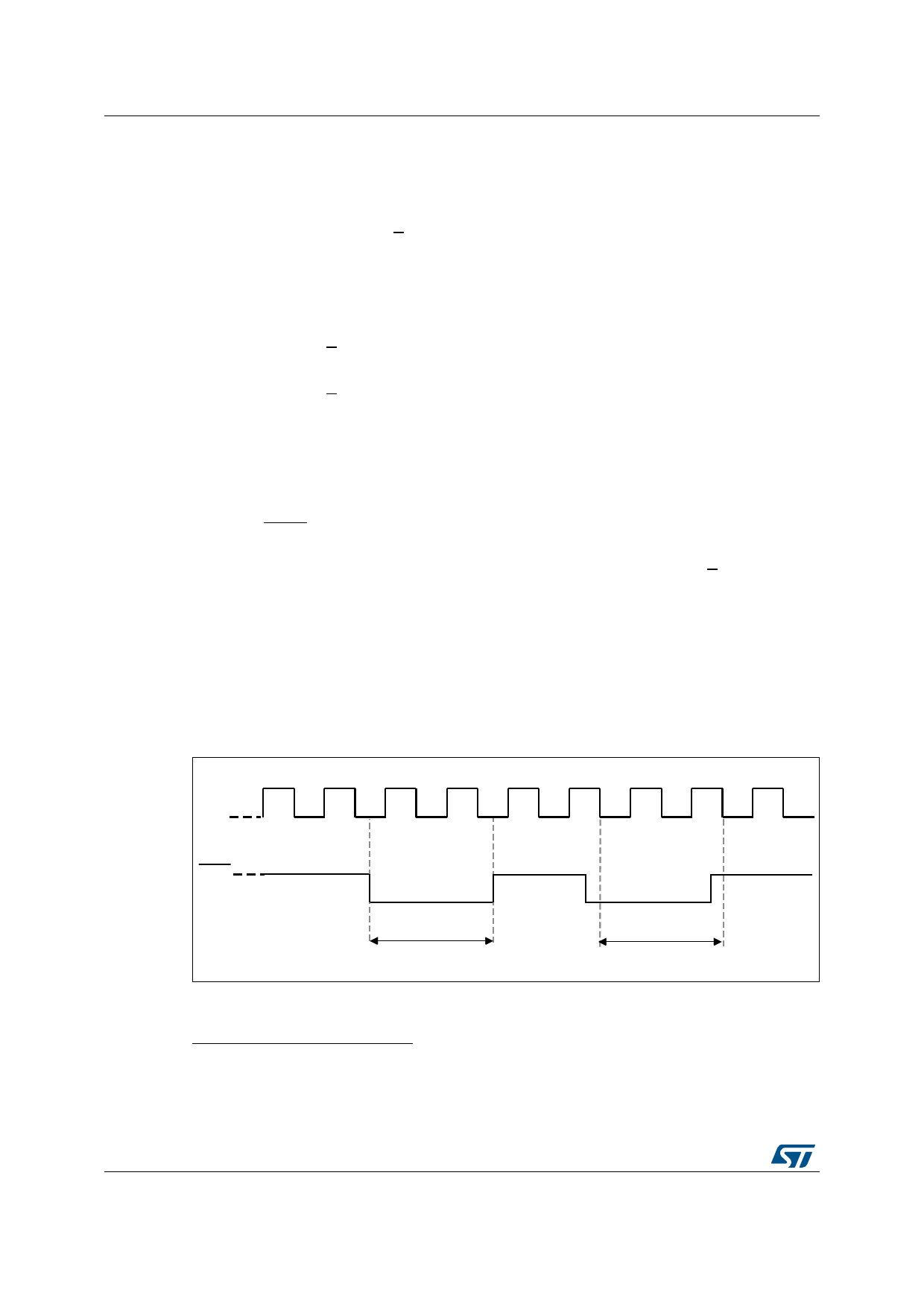

Figure 7. Hold condition activation

F

+2/'

+ROG

FRQGLWLRQ

+ROG

FRQGLWLRQ

DL

(

14/47

a. This resets the internal logic, except the WEL and WIP bits of the Status Register.

b. In the specific case where the device has shifted in a Write command (Inst + Address + data bytes, each data

byte being exactly 8 bits), deselecting the device also triggers the Write cycle of this decoded command.

DocID022580 Rev 5