CP2120 Ver la hoja de datos (PDF) - Silicon Laboratories

Número de pieza

componentes Descripción

Fabricante

CP2120 Datasheet PDF : 24 Pages

| |||

CP2120

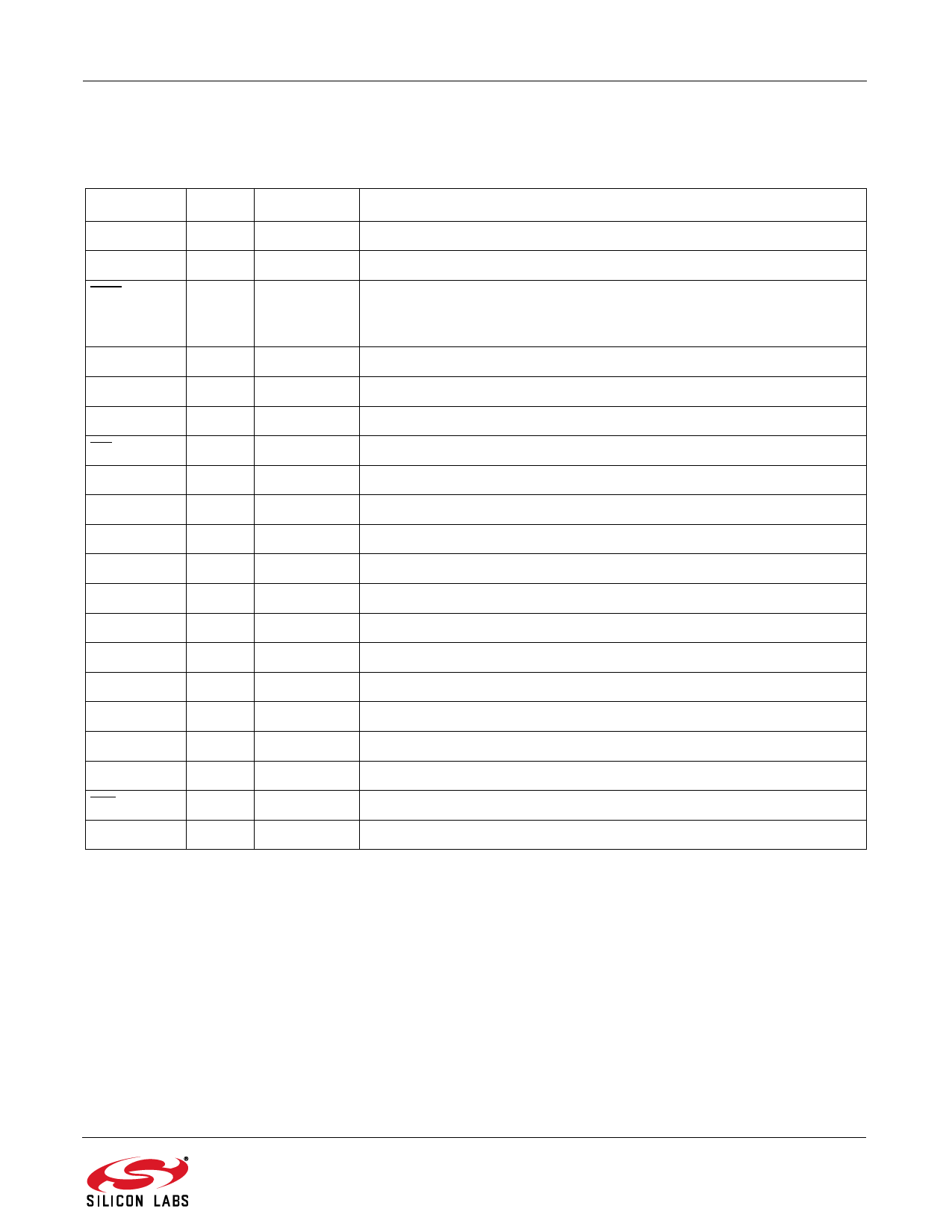

4. Pinout And Package Definition

4.1. Pin Out Chart

Name

VDD

GND

RST

SCLK

MISO

MOSI

CS

SDA

SCL

GPIO 0

GPIO 1

GPIO 2

GPIO 3

GPIO 4

GPIO 5

GPIO 6

GPIO 7

EINT

INT

NC

Pin #

Type

3

2

4

Digital I/O

1

Digital In

20

Digital Out

19

Digital In

18

Digital In

17

Digital I/O

16

Digital I/O

5

Digital I/O

12

Digital I/O

11

Digital I/O

10

Digital I/O

9

Digital I/O

8

Digital I/O

7

Digital I/O

6

Digital I/O

13

Digital I/O

14

Digital Out

15

Digital Out

Description

Power Supply Pin

Ground

Device Reset. Open-drain output of internal POR or VDD monitor. An

external source can initiate a system reset by driving this pin low for at

least 15 µs.

SPI Clock Input

SPI Slave Output

SPI Slave Input

SPI Slave Select

I2C Data Input/Output

I2C Clock Input/Output

General Purpose Configurable Digital Input/Output

General Purpose Configurable Digital Input/Output

General Purpose Configurable Digital Input/Output

General Purpose Configurable Digital Input/Output

General Purpose Configurable Digital Input/Output

General Purpose Configurable Digital Input/Output

General Purpose Configurable Digital Input/Output

General Purpose Configurable Digital Input/Output

Edge-Triggered Interrupt Source

CP2120 Interrupt Indicator

Not connected, leave floating

Rev. 1.0

5