ATMEGA645V-8MU Ver la hoja de datos (PDF) - Atmel Corporation

Número de pieza

componentes Descripción

Fabricante

ATMEGA645V-8MU Datasheet PDF : 29 Pages

| |||

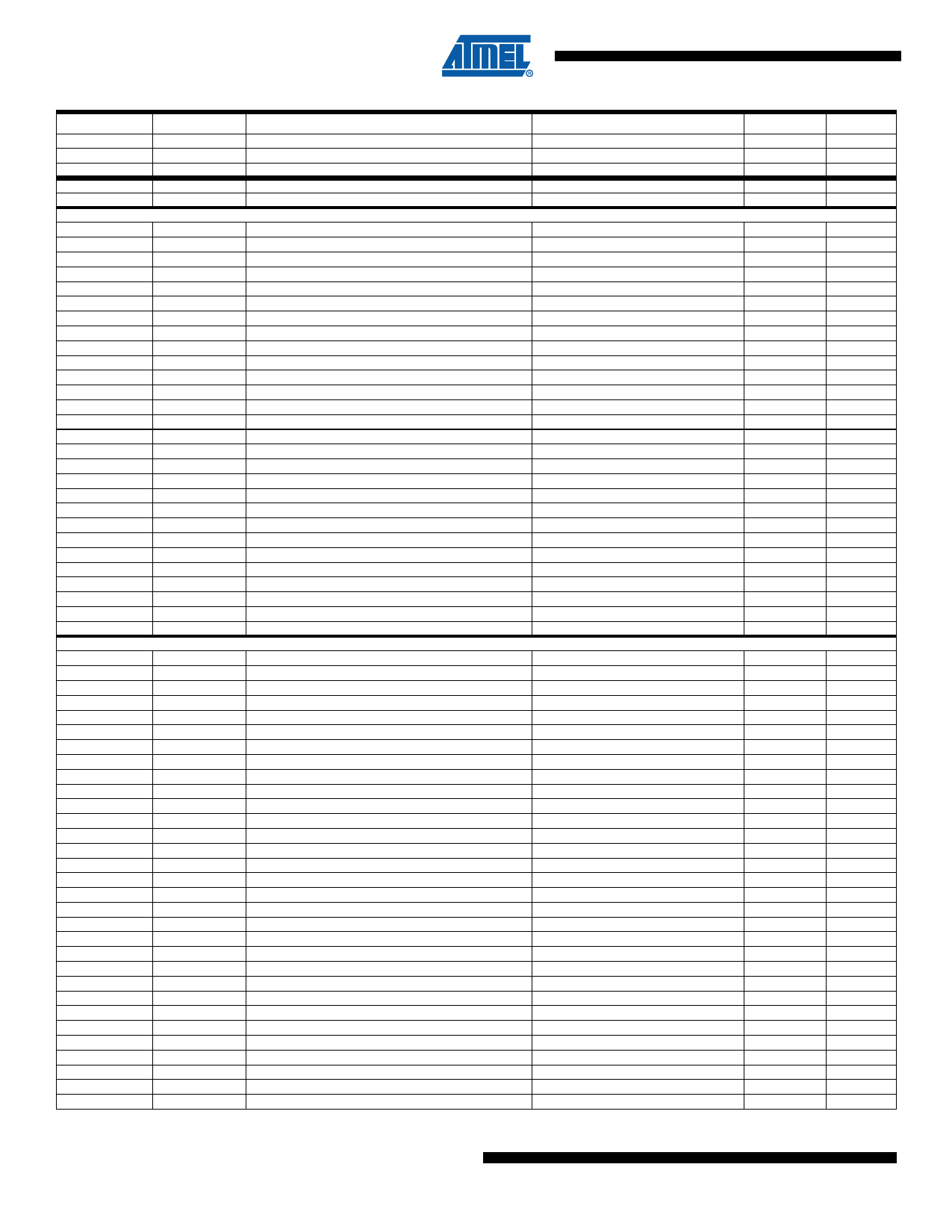

Mnemonics Operands

BRTC

k

BRVS

k

BRVC

k

BRIE

k

BRID

k

BIT AND BIT-TEST INSTRUCTIONS

SBI

P,b

CBI

P,b

LSL

Rd

LSR

Rd

ROL

Rd

ROR

Rd

ASR

Rd

SWAP

Rd

BSET

s

BCLR

s

BST

Rr, b

BLD

Rd, b

SEC

CLC

SEN

CLN

SEZ

CLZ

SEI

CLI

SES

CLS

SEV

CLV

SET

CLT

SEH

CLH

DATA TRANSFER INSTRUCTIONS

MOV

Rd, Rr

MOVW

Rd, Rr

LDI

Rd, K

LD

Rd, X

LD

Rd, X+

LD

Rd, - X

LD

Rd, Y

LD

Rd, Y+

LD

Rd, - Y

LDD

Rd,Y+q

LD

Rd, Z

LD

Rd, Z+

LD

Rd, -Z

LDD

Rd, Z+q

LDS

Rd, k

ST

X, Rr

ST

X+, Rr

ST

- X, Rr

ST

Y, Rr

ST

Y+, Rr

ST

- Y, Rr

STD

Y+q,Rr

ST

Z, Rr

ST

Z+, Rr

ST

-Z, Rr

STD

Z+q,Rr

STS

k, Rr

LPM

LPM

Rd, Z

LPM

Rd, Z+

SPM

Description

Branch if T Flag Cleared

Branch if Overflow Flag is Set

Branch if Overflow Flag is Cleared

Branch if Interrupt Enabled

Branch if Interrupt Disabled

Set Bit in I/O Register

Clear Bit in I/O Register

Logical Shift Left

Logical Shift Right

Rotate Left Through Carry

Rotate Right Through Carry

Arithmetic Shift Right

Swap Nibbles

Flag Set

Flag Clear

Bit Store from Register to T

Bit load from T to Register

Set Carry

Clear Carry

Set Negative Flag

Clear Negative Flag

Set Zero Flag

Clear Zero Flag

Global Interrupt Enable

Global Interrupt Disable

Set Signed Test Flag

Clear Signed Test Flag

Set Twos Complement Overflow.

Clear Twos Complement Overflow

Set T in SREG

Clear T in SREG

Set Half Carry Flag in SREG

Clear Half Carry Flag in SREG

Move Between Registers

Copy Register Word

Load Immediate

Load Indirect

Load Indirect and Post-Inc.

Load Indirect and Pre-Dec.

Load Indirect

Load Indirect and Post-Inc.

Load Indirect and Pre-Dec.

Load Indirect with Displacement

Load Indirect

Load Indirect and Post-Inc.

Load Indirect and Pre-Dec.

Load Indirect with Displacement

Load Direct from SRAM

Store Indirect

Store Indirect and Post-Inc.

Store Indirect and Pre-Dec.

Store Indirect

Store Indirect and Post-Inc.

Store Indirect and Pre-Dec.

Store Indirect with Displacement

Store Indirect

Store Indirect and Post-Inc.

Store Indirect and Pre-Dec.

Store Indirect with Displacement

Store Direct to SRAM

Load Program Memory

Load Program Memory

Load Program Memory and Post-Inc

Store Program Memory

14 ATmega325/3250/645/6450

Operation

if (T = 0) then PC ← PC + k + 1

if (V = 1) then PC ← PC + k + 1

if (V = 0) then PC ← PC + k + 1

if ( I = 1) then PC ← PC + k + 1

if ( I = 0) then PC ← PC + k + 1

I/O(P,b) ← 1

I/O(P,b) ← 0

Rd(n+1) ← Rd(n), Rd(0) ← 0

Rd(n) ← Rd(n+1), Rd(7) ← 0

Rd(0)←C,Rd(n+1)← Rd(n),C←Rd(7)

Rd(7)←C,Rd(n)← Rd(n+1),C←Rd(0)

Rd(n) ← Rd(n+1), n=0..6

Rd(3..0)←Rd(7..4),Rd(7..4)←Rd(3..0)

SREG(s) ← 1

SREG(s) ← 0

T ← Rr(b)

Rd(b) ← T

C←1

C←0

N←1

N←0

Z←1

Z←0

I←1

I←0

S←1

S←0

V←1

V←0

T←1

T←0

H←1

H←0

Rd ← Rr

Rd+1:Rd ← Rr+1:Rr

Rd ← K

Rd ← (X)

Rd ← (X), X ← X + 1

X ← X - 1, Rd ← (X)

Rd ← (Y)

Rd ← (Y), Y ← Y + 1

Y ← Y - 1, Rd ← (Y)

Rd ← (Y + q)

Rd ← (Z)

Rd ← (Z), Z ← Z+1

Z ← Z - 1, Rd ← (Z)

Rd ← (Z + q)

Rd ← (k)

(X) ← Rr

(X) ← Rr, X ← X + 1

X ← X - 1, (X) ← Rr

(Y) ← Rr

(Y) ← Rr, Y ← Y + 1

Y ← Y - 1, (Y) ← Rr

(Y + q) ← Rr

(Z) ← Rr

(Z) ← Rr, Z ← Z + 1

Z ← Z - 1, (Z) ← Rr

(Z + q) ← Rr

(k) ← Rr

R0 ← (Z)

Rd ← (Z)

Rd ← (Z), Z ← Z+1

(Z) ← R1:R0

Flags

None

None

None

None

None

None

None

Z,C,N,V

Z,C,N,V

Z,C,N,V

Z,C,N,V

Z,C,N,V

None

SREG(s)

SREG(s)

T

None

C

C

N

N

Z

Z

I

I

S

S

V

V

T

T

H

H

None

None

None

None

None

None

None

None

None

None

None

None

None

None

None

None

None

None

None

None

None

None

None

None

None

None

None

None

None

None

None

#Clocks

1/2

1/2

1/2

1/2

1/2

2

2

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

3

3

3

-

2570LS–AVR–08/07