M74HCT137 Ver la hoja de datos (PDF) - STMicroelectronics

Número de pieza

componentes Descripción

Fabricante

M74HCT137 Datasheet PDF : 11 Pages

| |||

M74HCT137

3 TO 8 LINE DECODER/LATCH (INVERTING)

s HIGH SPEED:

tPD =17ns (TYP.) at VCC = 4.5V

s LOW POWER DISSIPATION:

ICC = 4µA(MAX.) at TA=25°C

s SYMMETRICAL OUTPUT IMPEDANCE:

|IOH| = IOL = 4mA (MIN)

s BALANCED PROPAGATION DELAYS:

tPLH ≅ tPHL

s WIDE OPERATING VOLTAGE RANGE:

VCC (OPR) = 2V to 6V

s PIN AND FUNCTION COMPATIBLE WITH

74 SERIES 137

DESCRIPTION

The M74HCT137 is an high speed CMOS 3 TO 8

LINE DECODER/LATCH (INVERTING) fabricated

with silicon gate C2MOS technology.

This device is a 3 to 8 line decoder with latches on

the three address inputs. When GL goes from low

to high, the addresses present at the select inputs

(A, B, and C) is stored in the latches. As long as

GL remains high no address changes will be

recognized. Output enable pins G1 and G2,

control the state of the outputs independently of

the select or latch-enable inputs. All the outputs

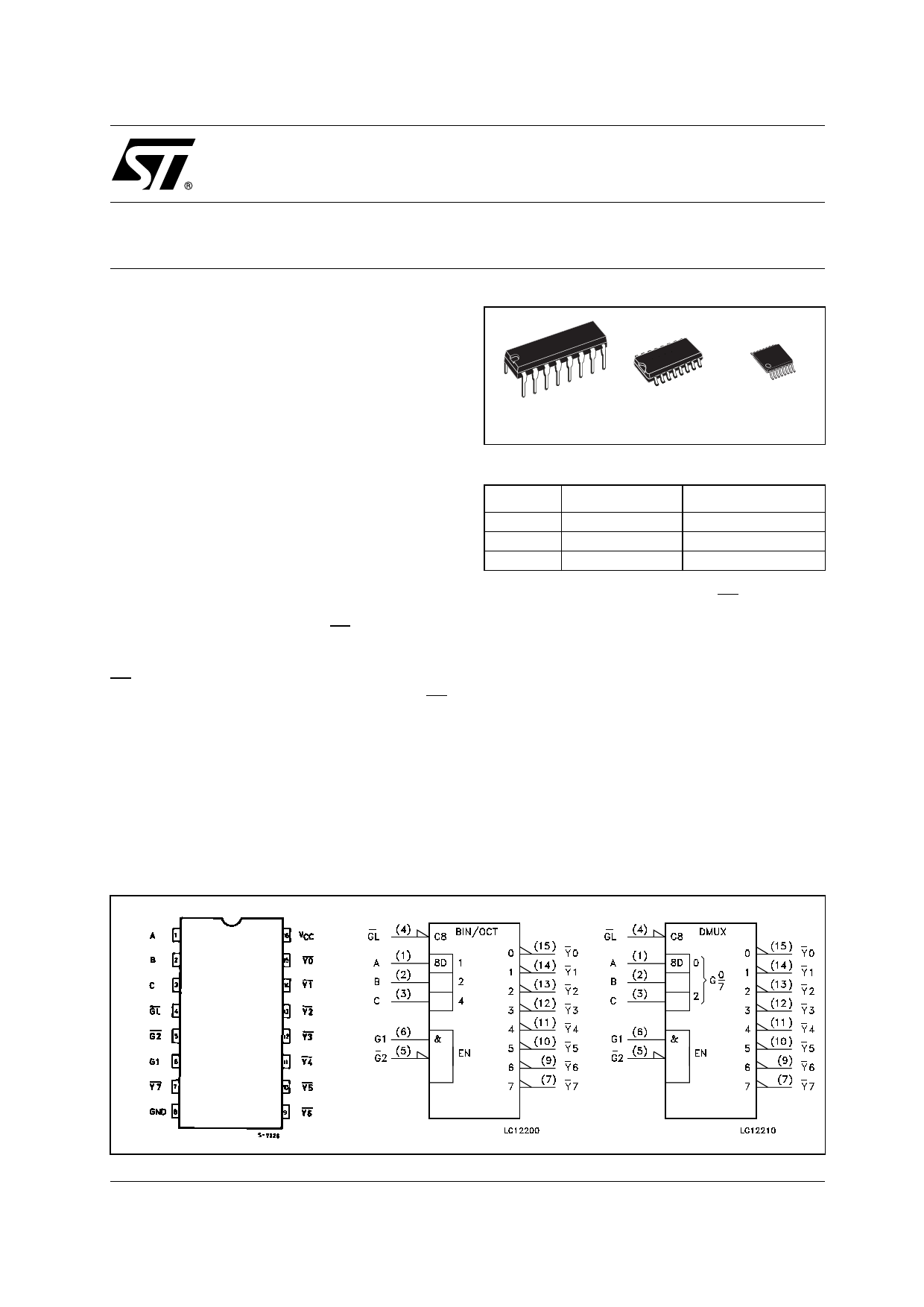

DIP

SOP

TSSOP

ORDER CODES

PACKAGE

TUBE

T&R

DIP

SOP

TSSOP

M74HCT137B1R

M74HCT137M1R M74HCT137RM13TR

M74HCT137TTR

are high unless G1 is high and G2 is low. The

74HCT137 is ideally suited for the implementation

of glitch-free decoders in stored-address

application in bus oriented systems.

All inputs are equipped with protection circuits

against static discharge and transient excess

voltage.

PIN CONNECTION AND IEC LOGIC SYMBOLS

September 2001

1/11