ADSP-21161NKCA-100(RevA) Ver la hoja de datos (PDF) - Analog Devices

Número de pieza

componentes Descripción

Fabricante

ADSP-21161NKCA-100 Datasheet PDF : 60 Pages

| |||

ADSP-21161N

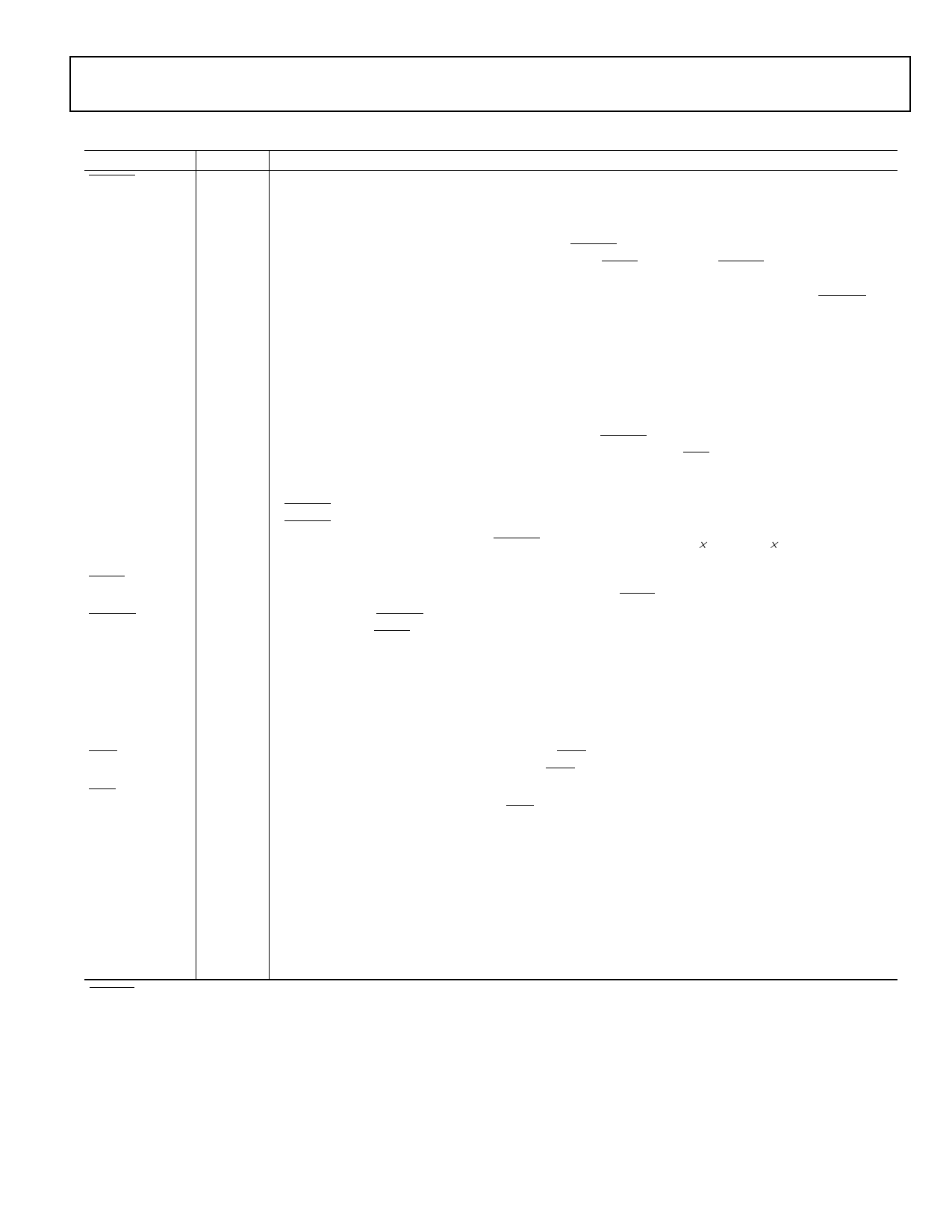

Table 2. Pin Function Descriptions (continued)

Pin

FSx

SPICLK

SPIDS

MOSI

MISO

LxDAT7–0

[DATA15–0]

LxCLK

LxACK

EBOOT

LBOOT

Type

Function

I/O

I/O

I

I/O (o/d)

I/O (o/d)

I/O

[I/O/T]

I/O

I/O

I

I

Transmit or Receive Frame Sync (Serial Ports 0, 1, 2, 3). The frame sync pulse initiates

shifting of serial data. This signal is either generated internally or externally. It can be active

high or low or an early or a late frame sync, in reference to the shifting of serial data.

Serial Peripheral Interface Clock Signal. Driven by the master, this signal controls the

rate at which data is transferred. The master may transmit data at a variety of baud rates.

SPICLK cycles once for each bit transmitted. SPICLK is a gated clock that is active during

data transfers, only for the length of the transferred word. Slave devices ignore the serial

clock if the slave select input is driven inactive (HIGH). SPICLK is used to shift out and

shift in the data driven on the MISO and MOSI lines. The data is always shifted out on one

clock edge of the clock and sampled on the opposite edge of the clock. Clock polarity and

clock phase relative to data are programmable into the SPICTL control register and define

the transfer format. SPICLK has a 50 kΩ internal pull-up resistor.

Serial Peripheral Interface Slave Device Select. An active low signal used to enable

slave devices. This input signal behaves like a chip select, and is provided by the master device

for the slave devices. In multimaster mode SPIDS signal can be asserted to a master device

to signal that an error has occurred, as some other device is also trying to be the master

device. If asserted low when the device is in master mode, it is considered a multimaster

error. For a single-master, multiple-slave configuration where FLAG3–0 are used, this pin

must be tied or pulled high to VDDEXT on the master device. For ADSP-21161N to ADSP-

21161N SPI interaction, any of the master ADSP-21161N’s FLAG3–0 pins can be used to

drive the SPIDS signal on the ADSP-21161N SPI slave device.

SPI Master Out Slave. If the ADSP-21161N is configured as a master, the MOSI pin

becomes a data transmit (output) pin, transmitting output data. If the ADSP-21161N is

configured as a slave, the MOSI pin becomes a data receive (input) pin, receiving input data.

In an ADSP-21161N SPI interconnection, the data is shifted out from the MOSI output pin

of the master and shifted into the MOSI input(s) of the slave(s). MOSI has an internal pull-

up resistor.

SPI Master In Slave Out. If the ADSP-21161N is configured as a master, the MISO pin

becomes a data receive (input) pin, receiving input data. If the ADSP-21161N is configured

as a slave, the MISO pin becomes a data transmit (output) pin, transmitting output data. In

an ADSP-21161N SPI interconnection, the data is shifted out from the MISO output pin

of the slave and shifted into the MISO input pin of the master. MISO has an internal pull-

up resistor. MISO can be configured as o/d by setting the OPD bit in the SPICTL register.

Note: Only one slave is allowed to transmit data at any given time.

Link Port Data (Link Ports 0–1).

For silicon revisions 1.2 and higher, each LxDAT pin has a keeper latch that is enabled when

used as a data pin; or a 20 kΩ internal pull-down resistor that is enabled or disabled by the

LxPDRDE bit of the LCTL register.

For silicon revisions 0.3, 1.0, and 1.1 each LxDAT pin has a 50 kΩ internal pull-down resistor

that is enabled or disabled by the LxPDRDE bit of the LCTL register.

Note: L1DAT7–0 are multiplexed with the DATA15–8 pins L0DAT7–0 are multiplexed with the

DATA7–0 pins. If link ports are disabled and are not used, these pins can be used as additional

data lines for executing instructions at up to the full clock rate from external memory. See

DATA47–16 for more information.

Link Port Clock (Link Ports 0–1). Each LxCLK pin has an internal pull-down 50 kΩ

resistor that is enabled or disabled by the LxPDRDE bit of the LCTL register.

Link Port Acknowledge (Link Ports 0–1). Each LxACK pin has an internal pull-down

50 kΩ resistor that is enabled or disabled by the LxPDRDE bit of the LCTL register.

EPROM Boot Select. For a description of how this pin operates, see the table in the BMS

pin description. This signal is a system configuration selection that should be hardwired.

Link Boot. For a description of how this pin operates, see the table in the BMS pin

description. This signal is a system configuration selection that should be hardwired.

REV. A

–15–