A42MX09-3TQG176I Ver la hoja de datos (PDF) - Microsemi Corporation

Número de pieza

componentes Descripción

Fabricante

A42MX09-3TQG176I Datasheet PDF : 142 Pages

| |||

40MX and 42MX FPGA Families

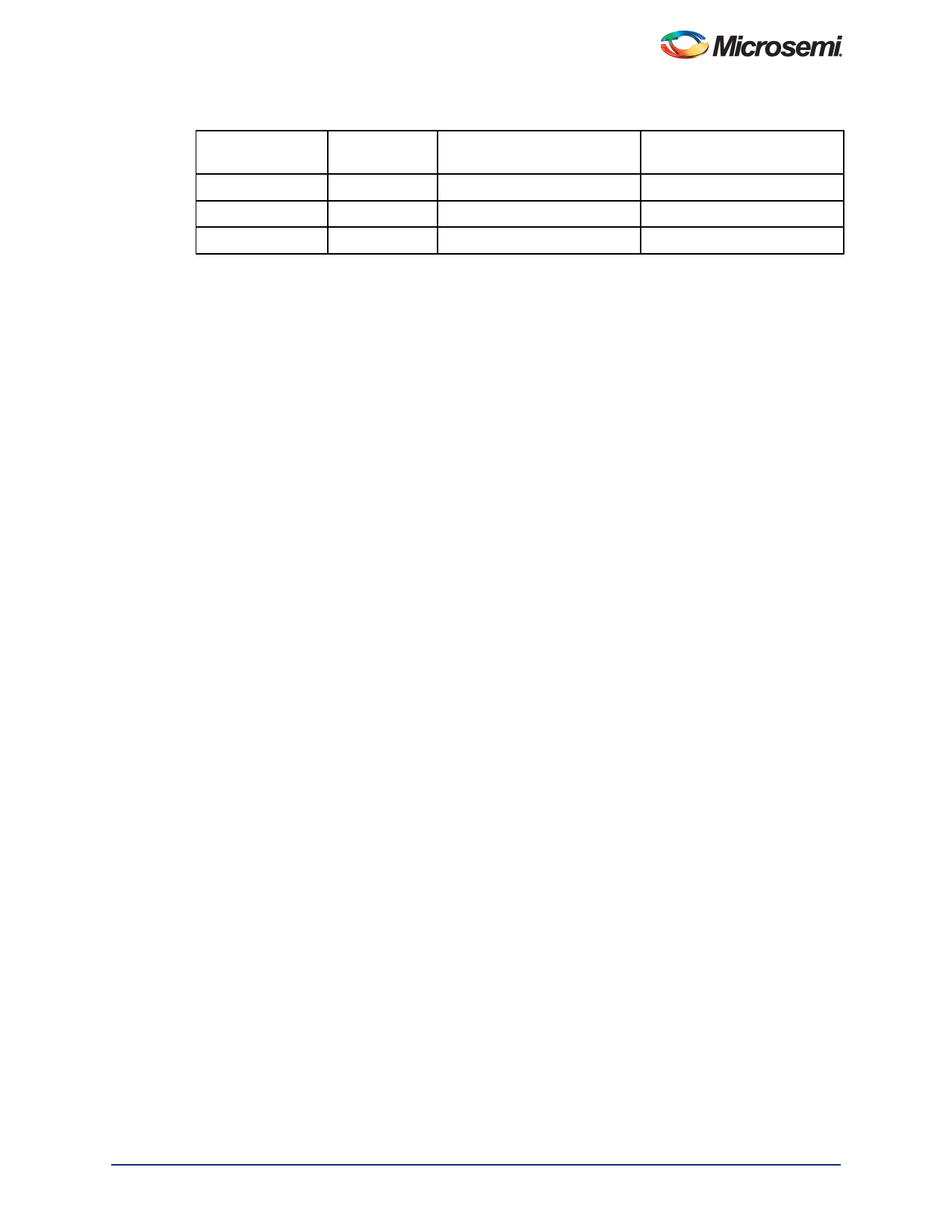

Table 1-2 • Device Configuration Options for Probe Capability

Security Fuse(s)

Programmed

No

Mode

LOW

PRA, PRB1

User I/Os2

SDI, SDO, DCLK1

User I/Os2

No

HIGH

Probe Circuit Outputs

Probe Circuit Inputs

Yes

–

Probe Circuit Secured

Probe Circuit Secured

Notes:

1. Avoid using SDI, SDO, DCLK, PRA and PRB pins as input or bidirectional ports. Since these pins are

active during probing, input signals will not pass through these pins and may cause contention.

2. If no user signal is assigned to these pins, they will behave as unused I/Os in this mode. See the "Pin

Descriptions" section on page 1-83 for information on unused I/O pins.

Design Consideration

It is recommended to use a series 70Ω termination resistor on every probe connector (SDI, SDO, MODE,

DCLK, PRA and PRB). The 70Ω series termination is used to prevent data transmission corruption

during probing and reading back the checksum.

IEEE Standard 1149.1 Boundary Scan Test (BST) Circuitry

42MX24 and 42MX36 devices are compatible with IEEE Standard 1149.1 (informally known as Joint

Testing Action Group Standard or JTAG), which defines a set of hardware architecture and mechanisms

for cost-effective board-level testing. The basic MX boundary-scan logic circuit is composed of the TAP

(test access port), TAP controller, test data registers and instruction register (Figure 1-13 on page 1-14).

This circuit supports all mandatory IEEE 1149.1 instructions (EXTEST, SAMPLE/PRELOAD and

BYPASS) and some optional instructions. Table 1-3 on page 1-14 describes the ports that control JTAG

testing, while Table 1-4 on page 1-14 describes the test instructions supported by these MX devices.

Each test section is accessed through the TAP, which has four associated pins: TCK (test clock input),

TDI and TDO (test data input and output), and TMS (test mode selector).

The TAP controller is a four-bit state machine. The '1's and '0's represent the values that must be

present at TMS at a rising edge of TCK for the given state transition to occur. IR and DR indicate that the

instruction register or the data register is operating in that state.

The TAP controller receives two control inputs (TMS and TCK) and generates control and clock signals

for the rest of the test logic architecture. On power-up, the TAP controller enters the Test-Logic-Reset

state. To guarantee a reset of the controller from any of the possible states, TMS must remain high for

five TCK cycles.

42MX24 and 42MX36 devices support three types of test data registers: bypass, device identification,

and boundary scan. The bypass register is selected when no other register needs to be accessed in a

device. This speeds up test data transfer to other devices in a test data path. The 32-bit device

identification register is a shift register with four fields (lowest significant byte (LSB), ID number, part

number and version). The boundary-scan register observes and controls the state of each I/O pin.

Each I/O cell has three boundary-scan register cells, each with a serial-in, serial-out, parallel-in, and

parallel-out pin. The serial pins are used to serially connect all the boundary-scan register cells in a

device into a boundary-scan register chain, which starts at the TDI pin and ends at the TDO pin. The

Revision 11

1- 13