A28F200BX-B Ver la hoja de datos (PDF) - Intel

Número de pieza

componentes Descripción

Fabricante

A28F200BX-B Datasheet PDF : 33 Pages

| |||

A28F200BX-T B

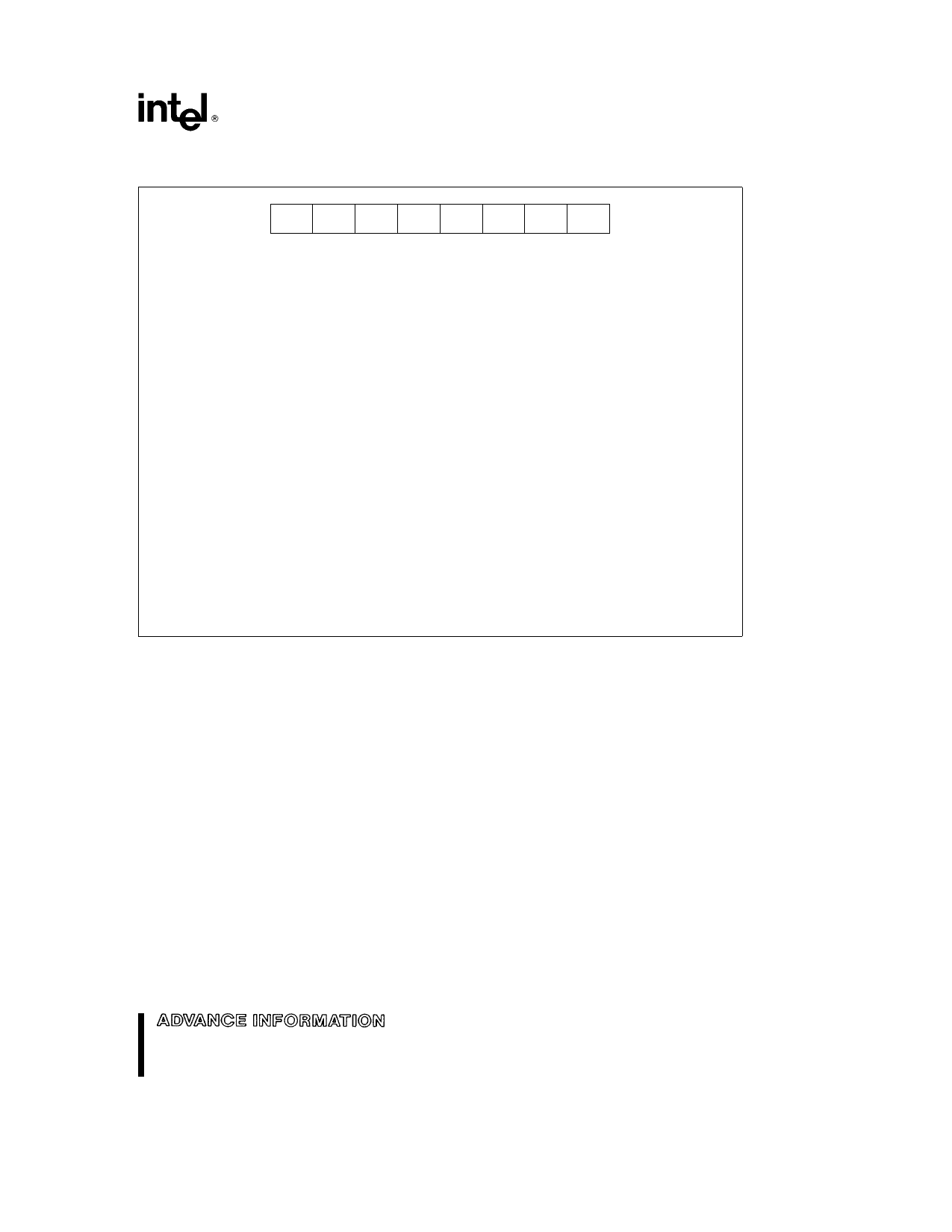

3 3 3 1 Status Register Bit Definition

Table 4 Status Register Definitions

WSMS ESS

ES

PS

7

6

5

4

SR 7 e WRITE STATE MACHINE STATUS

1 e Ready

0 e Busy

SR 6 e ERASE SUSPEND STATUS

1 e Erase Suspended

0 e Erase in Progress Completed

SR 5 e ERASE STATUS

1 e Error in Block Erasure

0 e Successful Block Erase

SR 4 e PROGRAM STATUS

1 e Error in Byte Word Program

0 e Successful Byte Word Program

SR 3 e VPP STATUS

1 e VPP Low Detect Operation Abort

0 e VPP OK

SR 2 – SR 0 e RESERVED FOR FUTURE ENHANCE-

MENTS

VPPS

R

R

R

3

2

1

0

NOTES

Write State Machine Status bit must first be checked to

determine byte word program or block erase completion

before the Program or Erase Status bits are checked for

success

When Erase Suspend is issued WSM halts execution

and sets both WSMS and ESS bits to ‘‘1’’ ESS bit re-

mains set to ‘‘1’’ until an Erase Resume command is is-

sued

When this bit is set to ‘‘1’’ WSM has applied the maxi-

mum number of erase pulses to the block and is still un-

able to successfully perform an erase verify

When this bit is set to ‘‘1’’ WSM has attempted but failed

to Program a byte or word

The VPP Status bit unlike an A D converter does not

provide continuous indication of VPP level The WSM in-

terrogates the VPP level only after the byte write or block

erase command sequences have been entered and in-

forms the system if VPP has not been switched on The

VPP Status bit is not guaranteed to report accurate feed-

back between VPPL and VPPH

These bits are reserved for future use and should be

masked out when polling the Status Register

3 3 3 2 Clearing the Status Register

Certain bits in the status register are set by the write

state machine and can only be reset by the system

software These bits can indicate various failure con-

ditions By allowing the system software to control

the resetting of these bits several operations may

be performed (such as cumulatively programming

several bytes or erasing multiple blocks in se-

quence) The status register may then be read to

determine if an error occurred during that program-

ming or erasure series This adds flexibility to the

way the device may be programmed or erased To

clear the status register the Clear Status Register

command is written to the CUI Then any other

command may be issued to the CUI Note again that

before a read cycle can be initiated a Read Array

command must be written to the CUI to specify

whether the read data is to come from the array

status register or Intelligent Identifier

3 3 4 PROGRAM MODE

Program is executed by a two-write sequence The

Program Setup command is written to the CUI fol-

lowed by a second write which specifies the address

and data to be programmed The write state ma-

chine will execute a sequence of internally timed

events to

1 Program the desired bits of the addressed memo-

ry word (byte) and

2 Verify that the desired bits are sufficiently pro-

grammed

Programming of the memory results in specific bits

within a byte or word being changed to a ‘‘0’’

If the user attempts to program ‘‘1’’s there will be no

change of the memory cell content and no error oc-

curs

Similar to erasure the status register indicates

whether programming is complete While the pro-

gram sequence is executing bit 7 of the status regis-

ter is a ‘‘0’’ The status register can be polled by

15