MAX4516CSA Ver la hoja de datos (PDF) - Maxim Integrated

Número de pieza

componentes Descripción

Fabricante

MAX4516CSA Datasheet PDF : 8 Pages

| |||

Dual-Supply, Low-On-Resistance,

SPST, CMOS Analog Switches

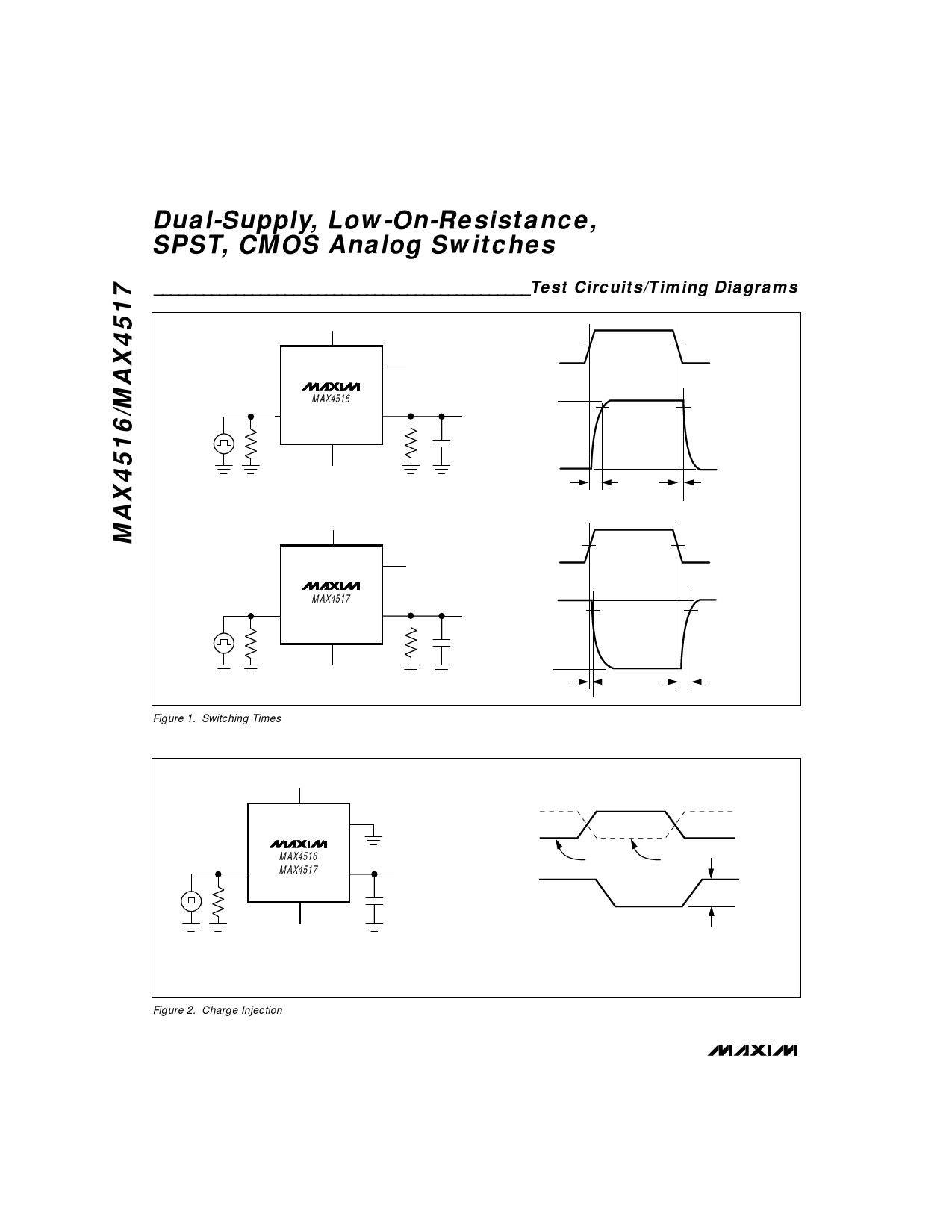

______________________________________________Test Circuits/Timing Diagrams

V+

V+

NO

VNO

VIN

IN

50Ω

MAX4516

COM

V-

300Ω

V-

VOUT

35pF

V+

VIN

0V

VNO PEAK

VOUT

tON

50%

90%

90%

tOFF

V+

V+

NC

VNC

VIN

IN

50Ω

MAX4517

COM

V-

300Ω

V-

Figure 1. Switching Times

VOUT

35pF

V+

VIN

0V

VNC PEAK

VOUT

0V

tOFF

50%

90%

90%

tON

V+

VIN

IN

50Ω

V+

NO

or

NC

MAX4516

MAX4517 COM

V-

V-

VNO or VNC = 0V

VOUT

CL

1000pF

V+

VIN

0V

VOUT

MAX4516

MAX4517

∆VOUT

∆VOUT IS THE MEASURED VOLTAGE DUE TO CHARGE TRANSFER

ERROR Q WHEN THE CHANNEL TURNS OFF.

Q = ∆VOUT x CL

Figure 2. Charge Injection

6 _______________________________________________________________________________________