CXK77B3610GB Ver la hoja de datos (PDF) - Sony Semiconductor

Número de pieza

componentes Descripción

Fabricante

CXK77B3610GB Datasheet PDF : 16 Pages

| |||

CXK77B3610GB

Test Mode Description

Fuctional Description

The CXK77B3610 provides JTAG boundary scan interface using IEEE std. 1149.1 protocol. The test mode is

intended to provided a mechanism for testing the interconnect between master (processor, controller, etc.),

SRAMs other components and print circuit board.

In conformance with IEEE std. 1149.1, the CXK77B3610 contains a TAP controller, Instruction register,

Boundary scan register and Bypass register.

Test Access Port (TAP)

4 pins as defined in Pin Description table are used to perform JTAG functions. TDI input pin is used to scan

test data serially into one of three registers (Instruction register, Boundary scan register and Bypass register).

TDO is output pin used to scan test data serially out. The TDI send the data into LSB of selected register and

the MSB of the selected register feeds the data to TDO. TMS input pin controls the state transition of 16 state

TAP controller as specified in IEEE std. 1149.1. Inputs on TDI, TMS are registered on the rising edge of TCK

clock and the output data on TDO is presented on the falling edge of TCK. TDO driver is in active state only

when TAP conroller is in Shift-IR state or in Shift-DR state.

TAP Controller

16 state controller is implemented as specified in IEEE std. 1149.1.

The controller enter reset state in one of three ways:

1. Power up

2. Apply logic 1 on TMS input pin on 5 consecutive TCK rising edges.

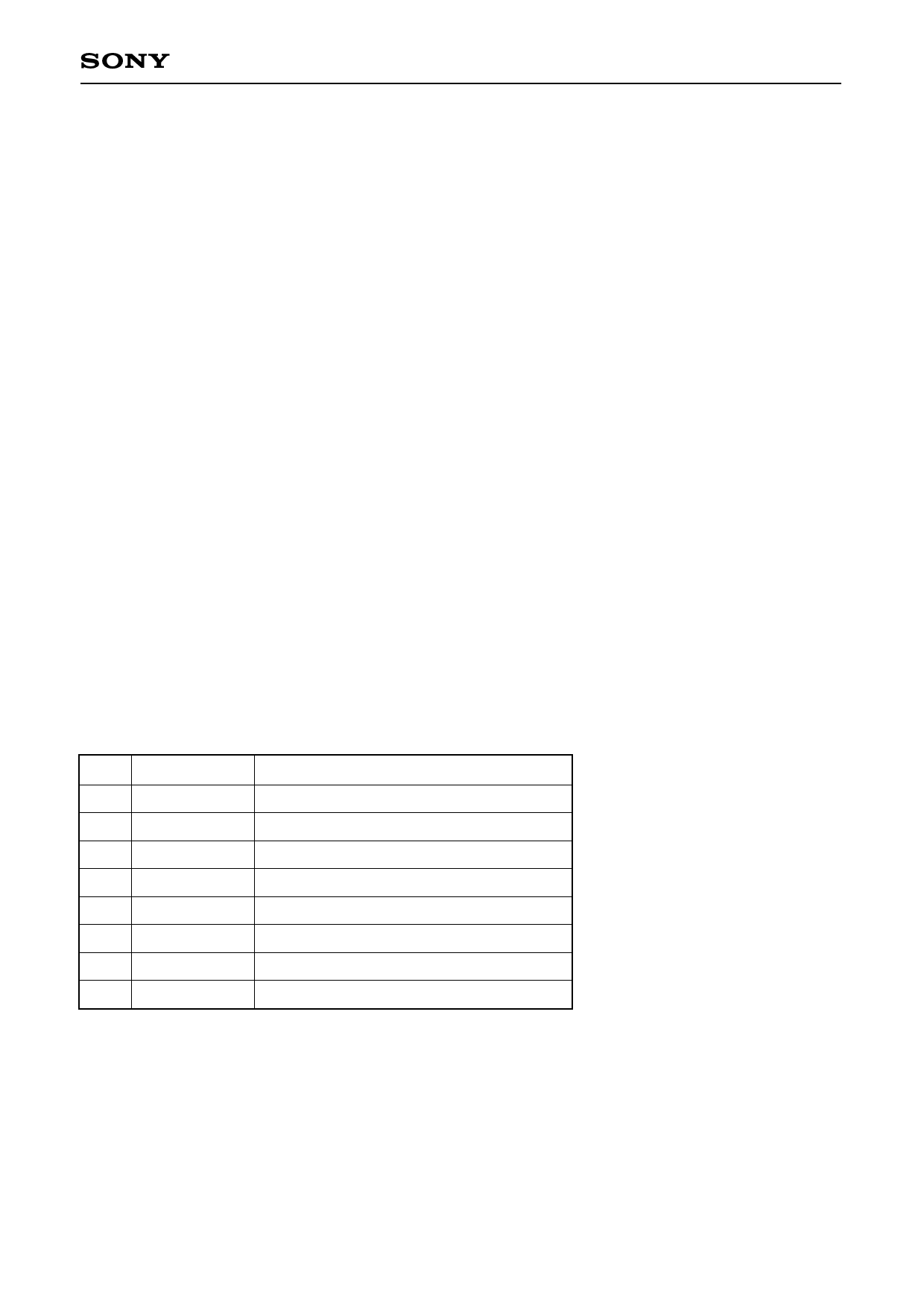

Instruction Resister (3 bits)

The JTAG Instruction resister is consisted of shift resister stage and parallel output latch. The register is 3 bits

wide and is encoded as follow:

Octal MSB LSB

Instruction

0

0 0 0 Bypass

1

0 0 1 IDCODE. read device ID

2

0 1 0 Sample-Z. Sample Inputs and tri-state DQs

3

0 1 1 Bypass

4

1 0 0 Sample. Sample Inputs.

5

1 0 1 Private. Manufacturer use only.

6

1 1 0 Bypass

7

1 1 1 Bypass

Bypass Register (1 bit)

The Bypass Register is one bit wide and is connected electrically between TDI and TDO and provides the

minimum length serial path between TDI and TDO.

– 13 –