Q67100-H3765 Ver la hoja de datos (PDF) - Siemens AG

NГәmero de pieza

componentes DescripciГіn

Fabricante

Q67100-H3765 Datasheet PDF : 26 Pages

| |||

SLx 24C64

3

I2C-Bus Characteristics

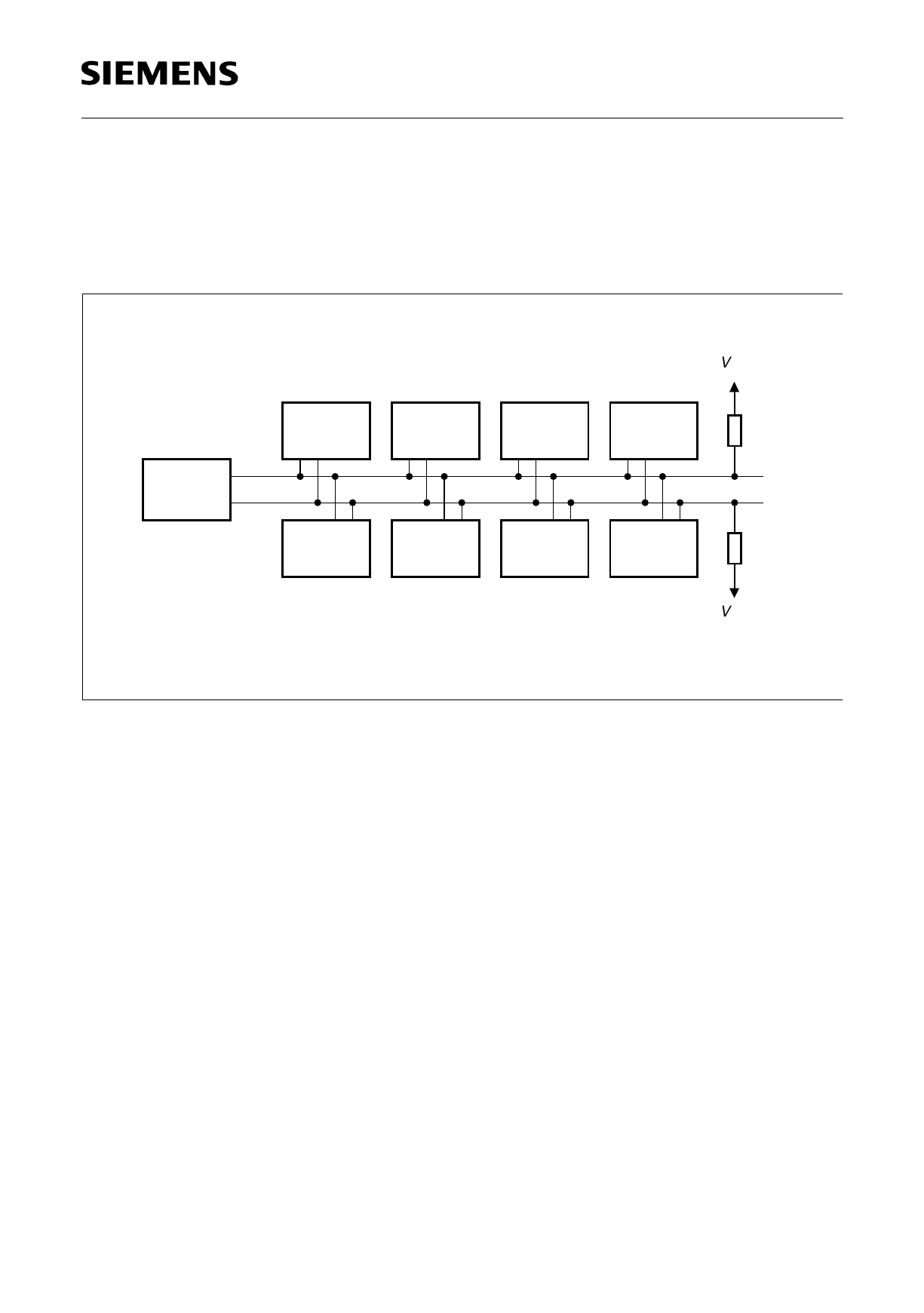

Access to the SLx 24C64 device is given via the I2C bus. This bidirectional bus consists

of two wires SCL and SDA for clock and data. The protocol is master/slave oriented,

where the serial EEPROM always takes the role of a slave.

Master

SCL

SDA

Slave 1

Slave 5

Slave 2

Slave 6

Slave 3

Slave 7

VCC

Slave 4

Slave 8

VCC

IES02183

Figure 3

Bus Configuration

Master

Device that initiates the transfer of data and provides the clock for transmit

and receive operations.

Slave

Device addressed by the master, capable of receiving and transmitting

data.

Transmitter The device using the SDA as output is defined as the transmitter. Due to

the open drain characteristic of the SDA output the device applying a low

level wins.

Receiver The device using the SDA as input is defined as the receiver.

Semiconductor Group

7

Preliminary 1998-07-27